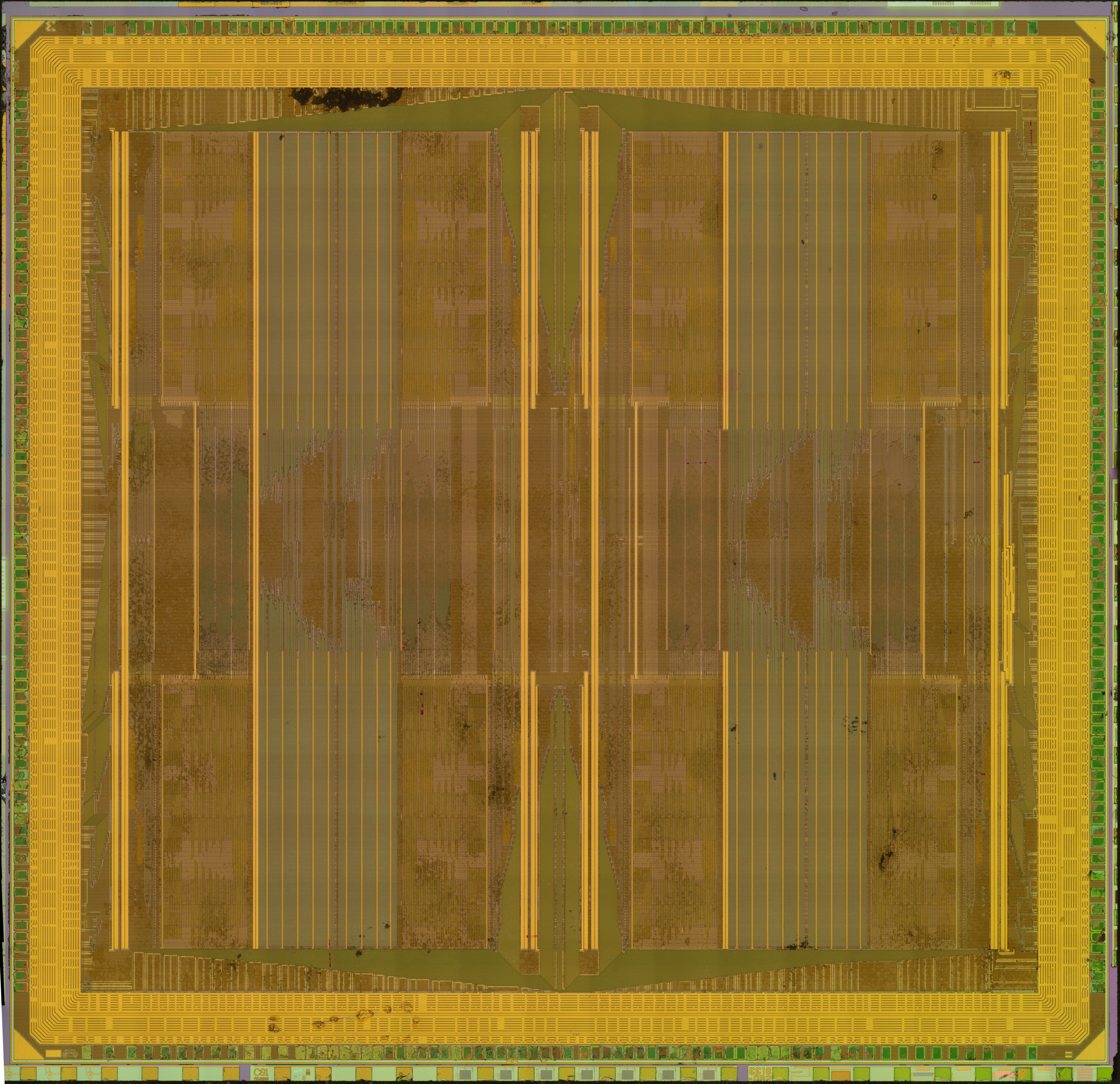

vendor:xilinx:xc2c

Xilinx CoolRunner-II CPLD family

Made on a 180nm process by UMC 1), 4-5 2) aluminum metal layers depending on device density. It appears that the 128 and smaller are 4 layers and the 256 and larger are 5.

Full RE of the family (focusing on the 32a) is in progress but there are no immediate plans to release.

| XC2C32A (3.24 mm2, 4 metal) | XC2C64A (4.61 mm2, 4 metal) | XC2C128 (9.59 mm2, 4 metal) | XC2C256 (15.54 mm2, 5 metal) | XC2C384 (30.50 mm2, 5 metal) | XC2C512 |

|---|---|---|---|---|---|

X8370 (rev A) |  X8380 (rev A) |  X7440 (rev B) |  X7410 (rev C) |  X7450 (rev ??) |  |

Thumbnail scale: 5 μm/pixel

vendor/xilinx/xc2c.txt · Last modified: 2024/01/21 18:39 by azonenberg