azonenberg:xilinx:xc2c32a

Table of Contents

Xilinx CoolRunner-II CPLD with 32 macrocells. The -A version supports two I/O banks while the baseline XC2C32 only has one.

180nm 4-metal process.

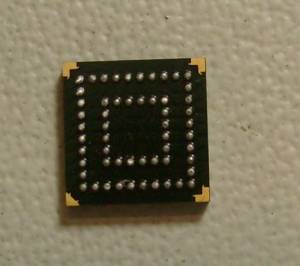

Package

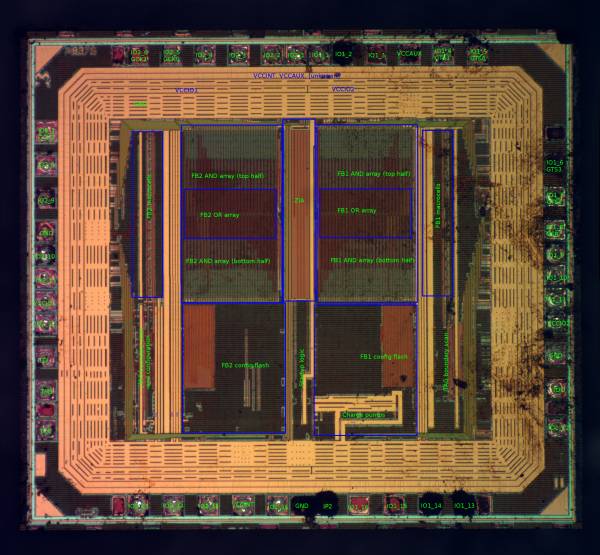

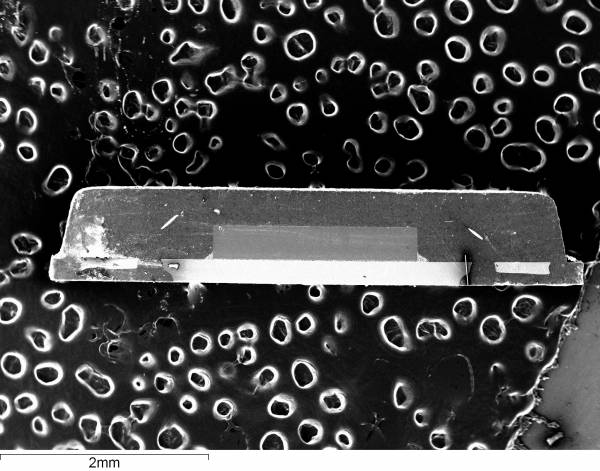

Die overview (metal 4)

Plan view closeups (metal 4)

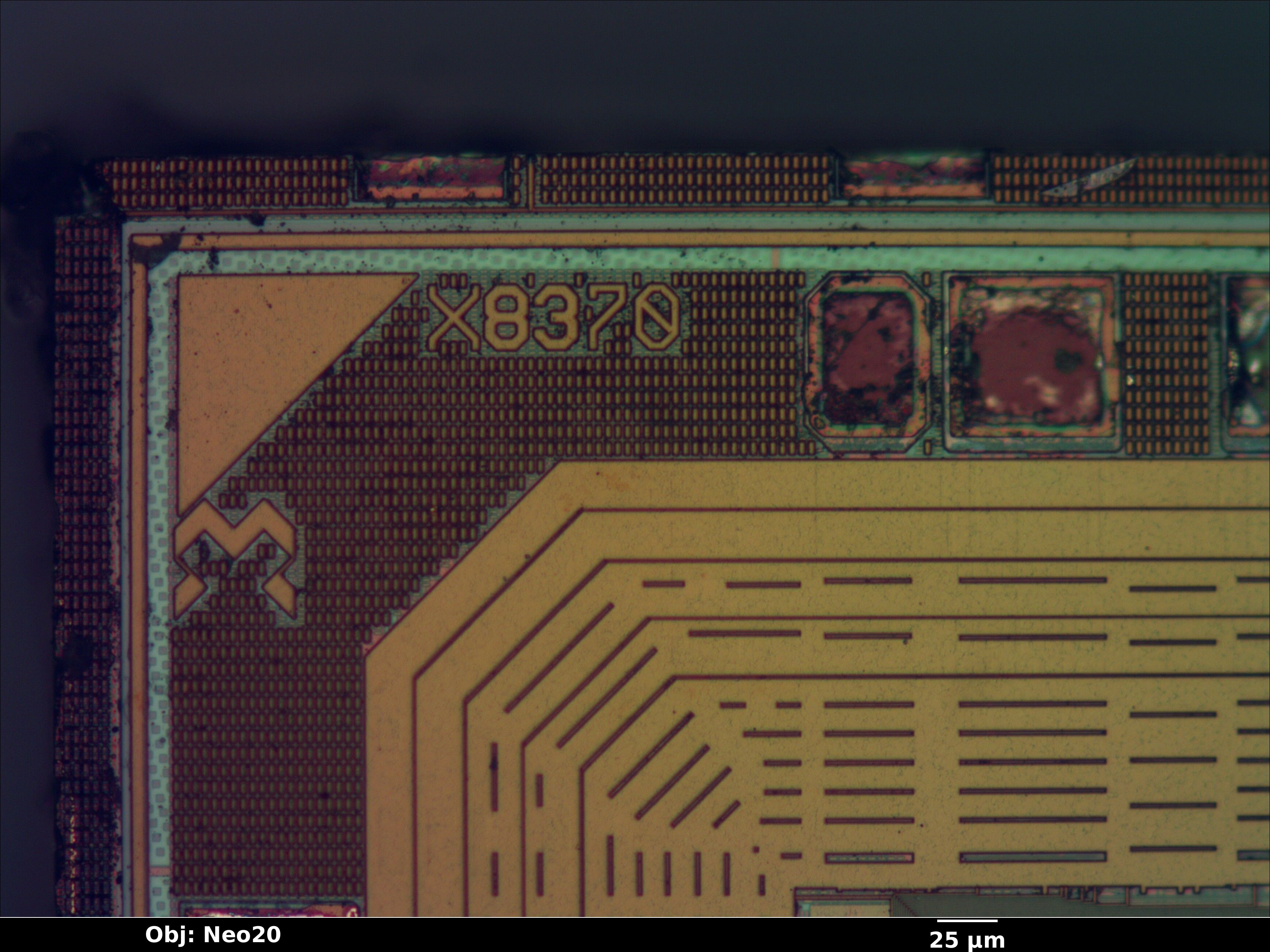

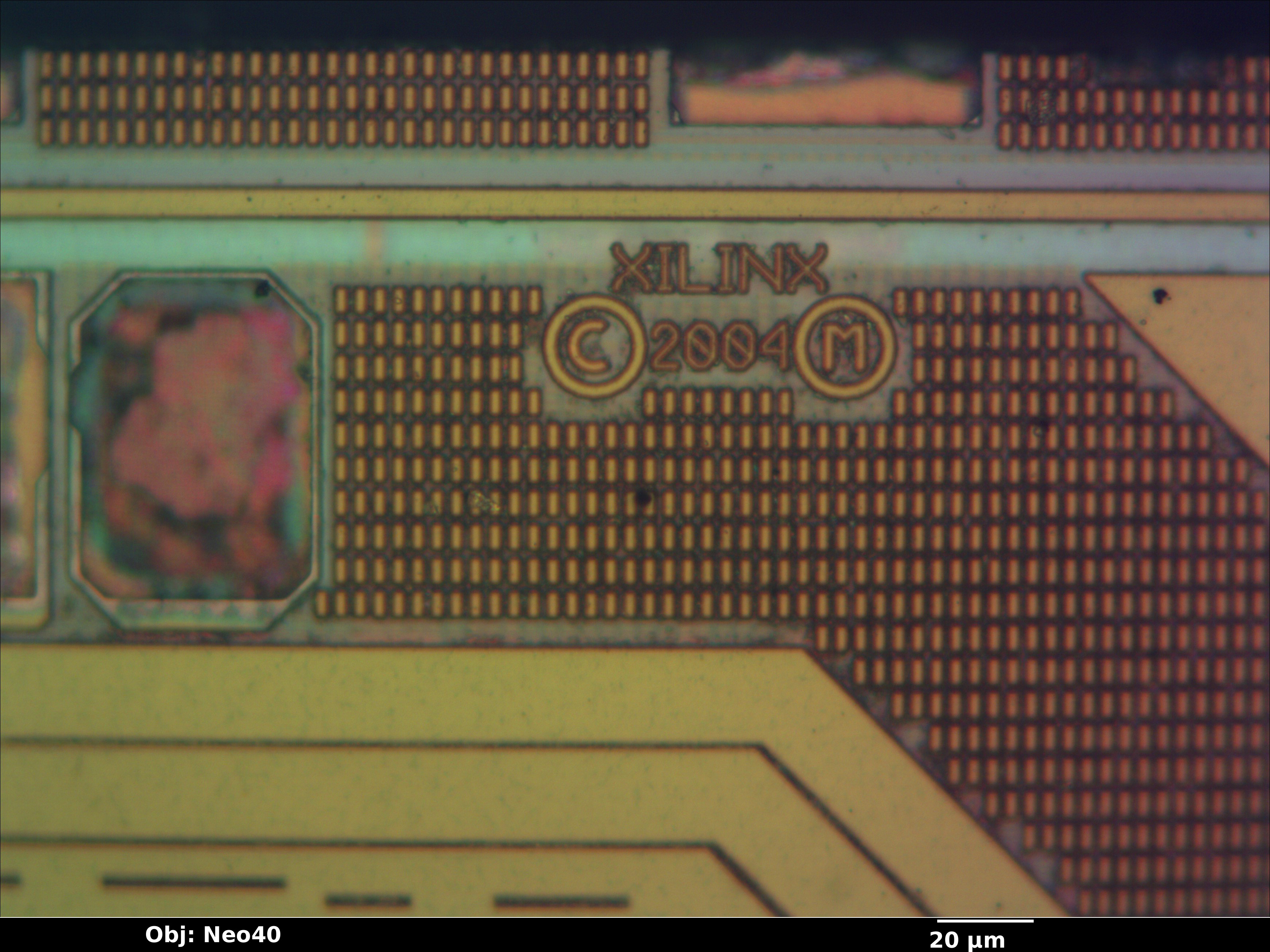

Die logo

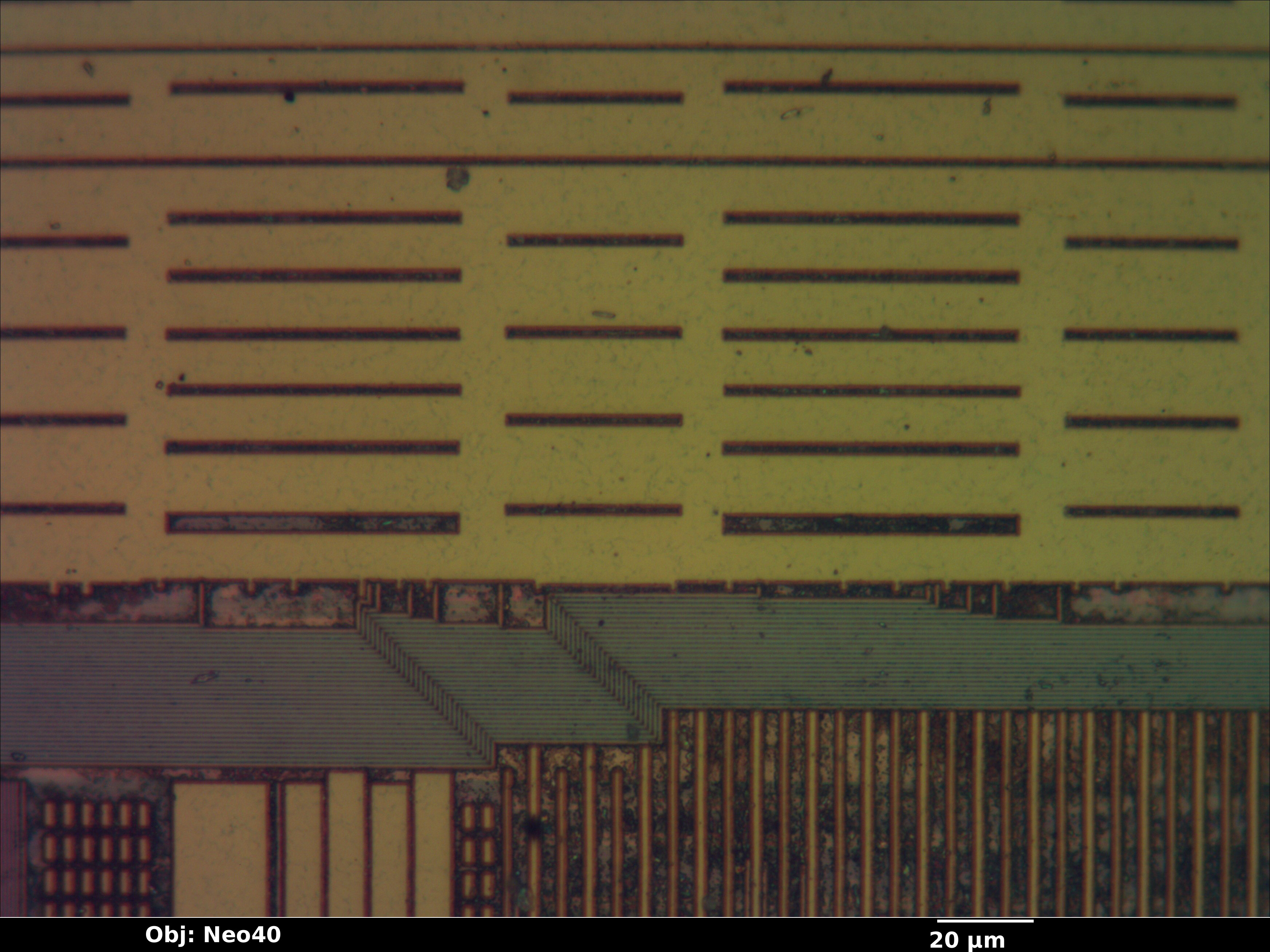

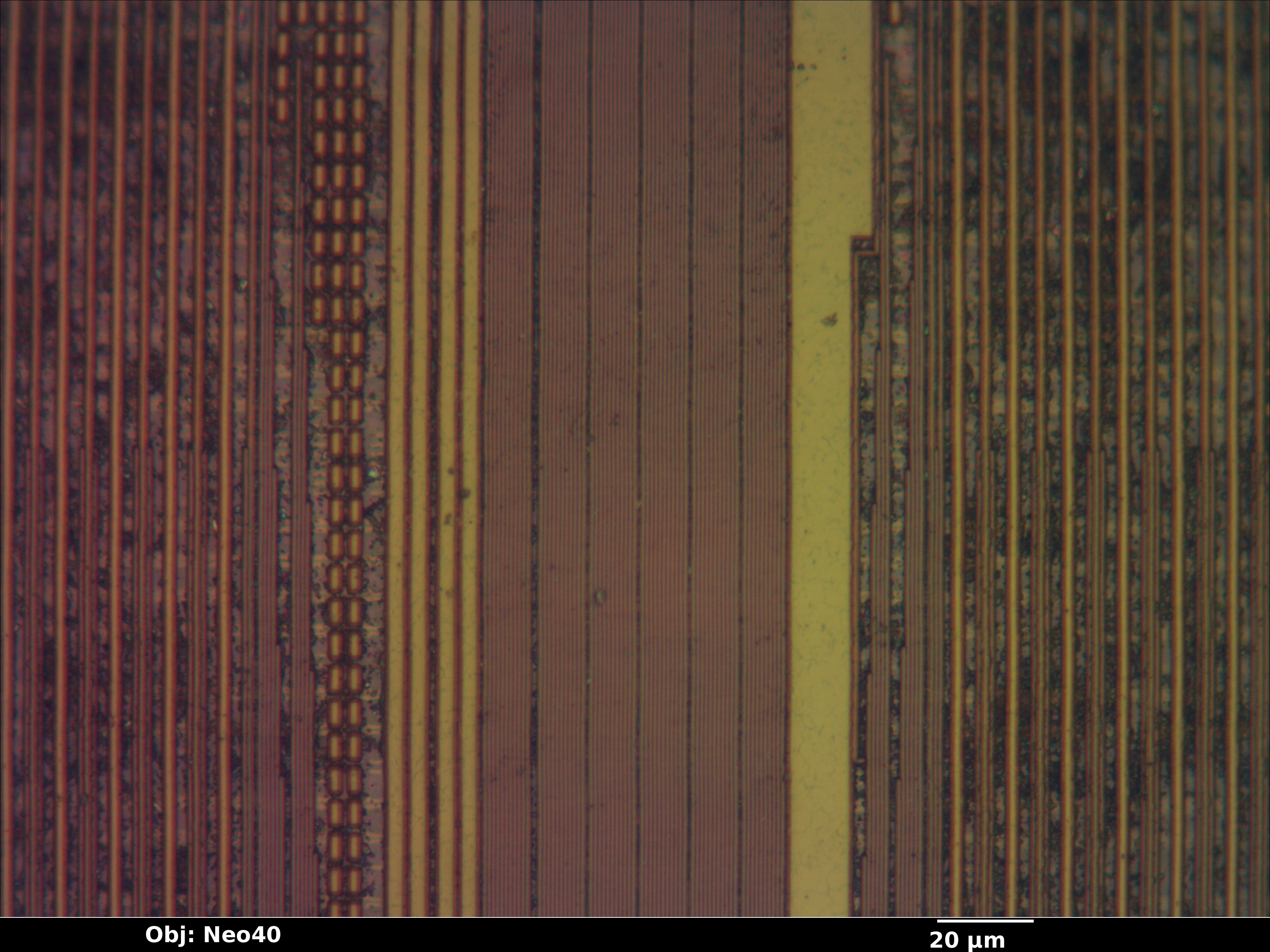

Output bus from function block 2 macrocells to I/O bank 1

Copyright notice (upside-down in bottom left corner)

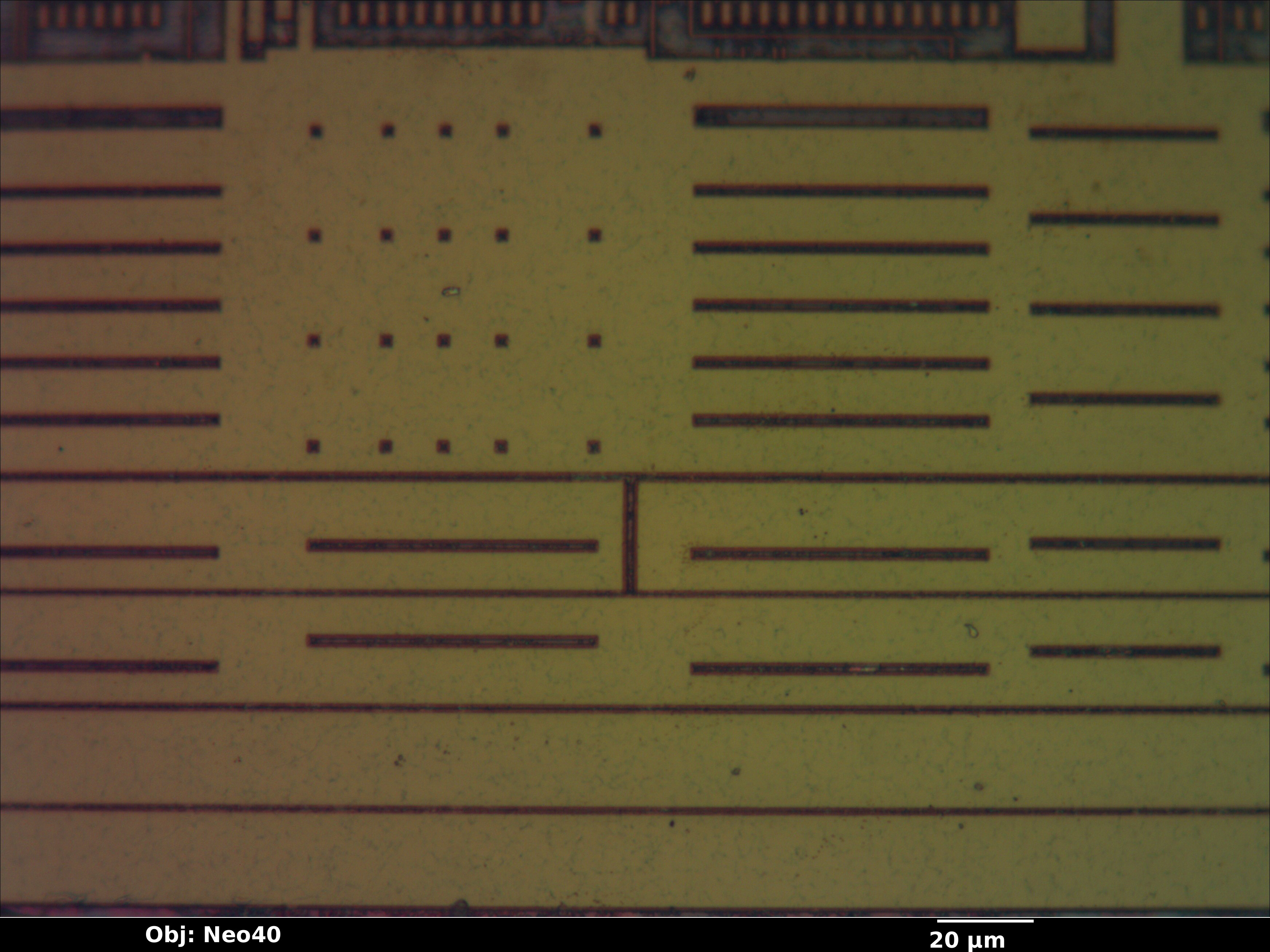

VCCIO junction

Junction between VCCIO1 (left) and VCCIO2 (right) at bottom center of die. Note vias from ground ring to ground pad at bottom.

ZIA wiring

Maps

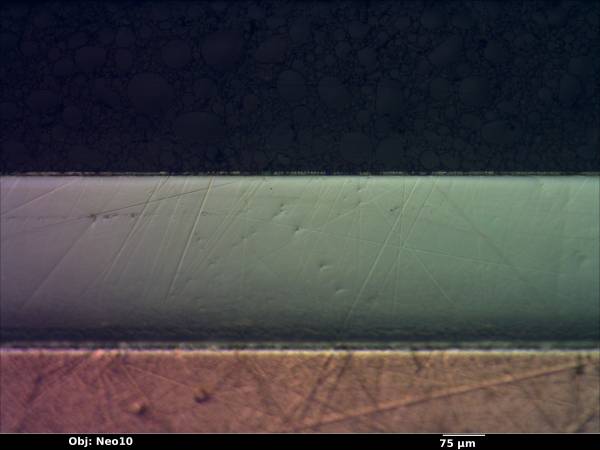

Cross sections

azonenberg/xilinx/xc2c32a.txt · Last modified: 2015/01/04 22:50 by 127.0.0.1