Table of Contents

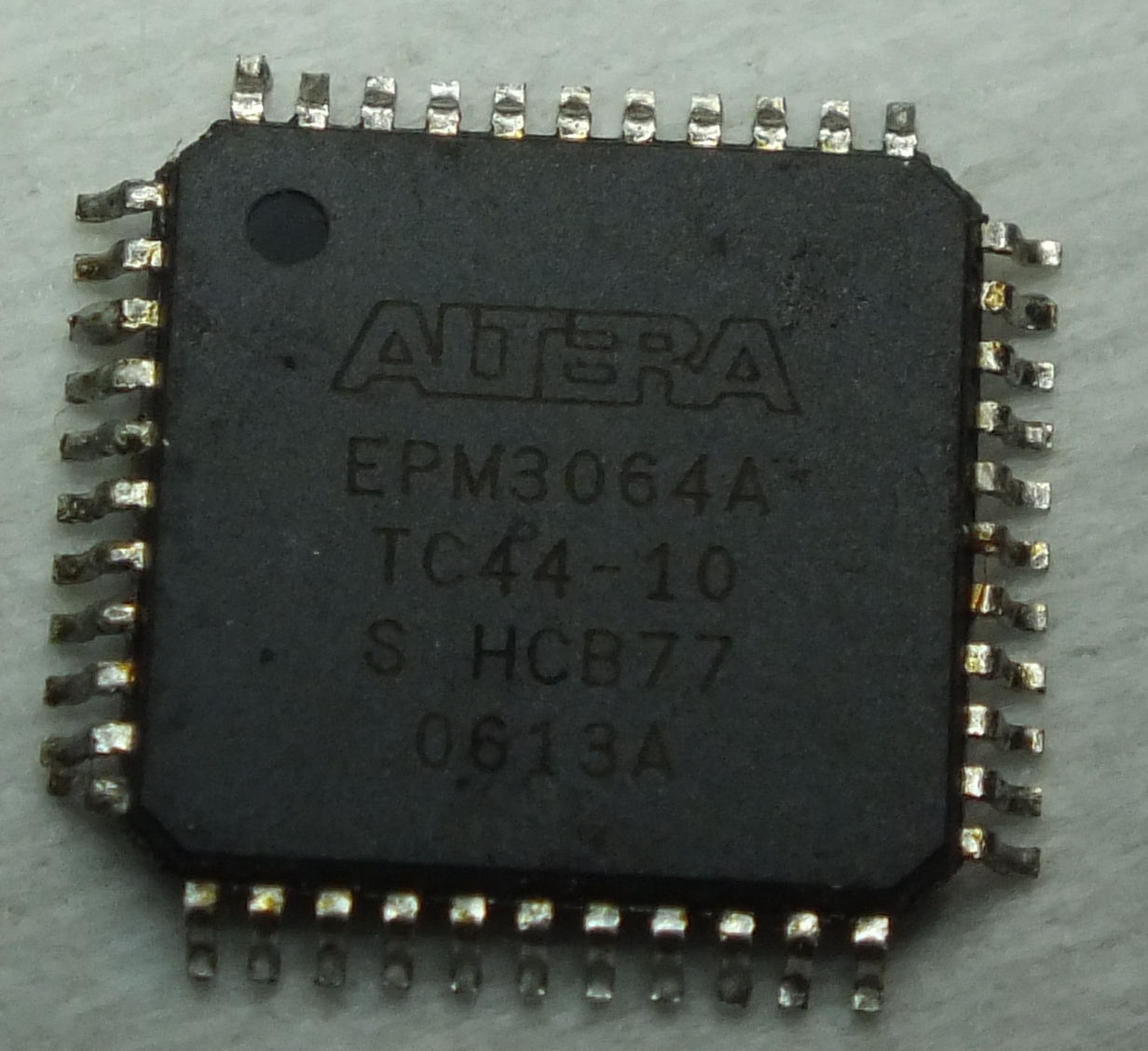

64-macrocell MAX 3000A series product term CPLD.

The MAX 3000A series was originally produced on TSMC's 350nm 4-metal process and was shrunk to 300nm in 2001.

Architecture

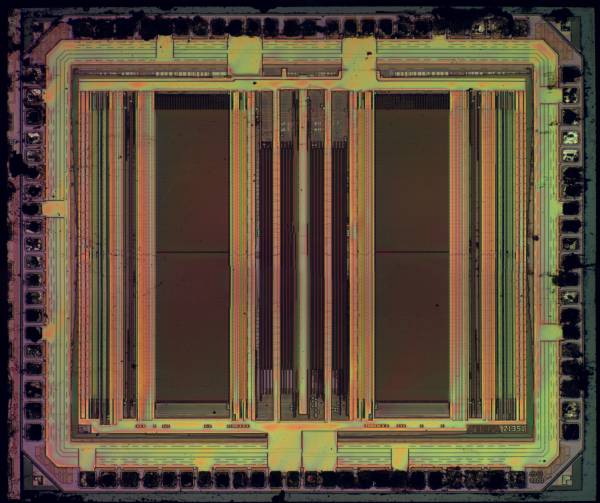

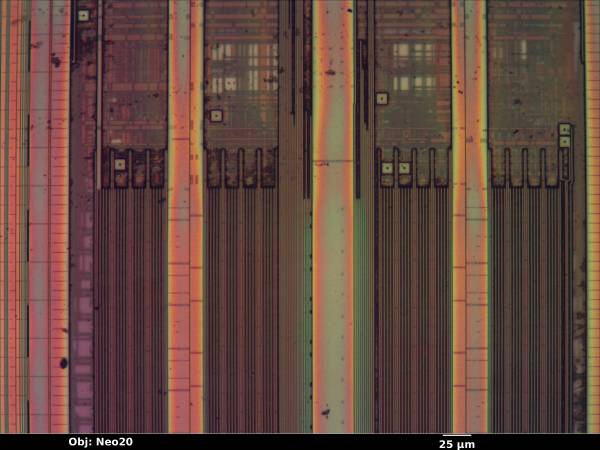

Four 16-macrocell logic array blocks organized in a 2×2 grid.

Unlike most Xilinx devices, the MAX 3000A family has a limited number (6 or 10) of output enables and cannot tristate each output pin independently.

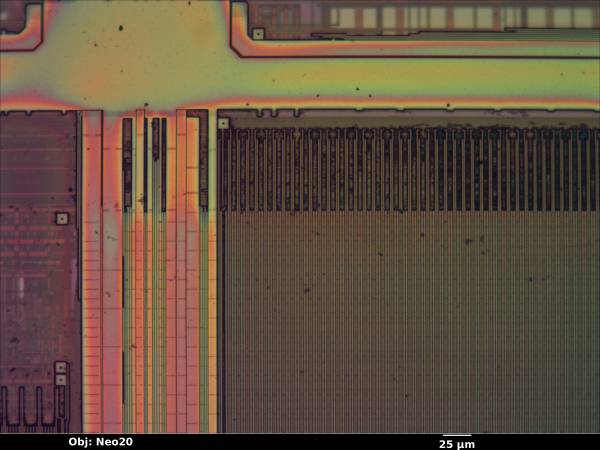

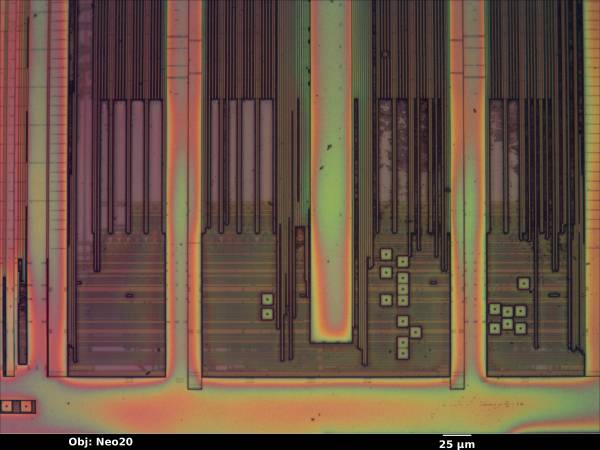

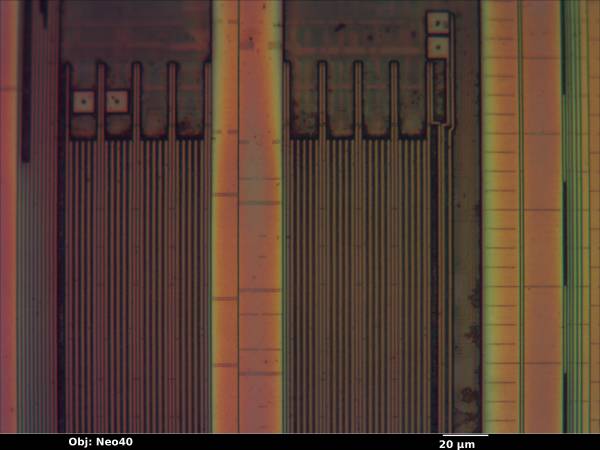

The product term array seems similar to the Xilinx XC9500XL family: 36 inputs from global routing feeding a large sense-amplifier-based programmable AND array, followed by a semi-fixed OR array.

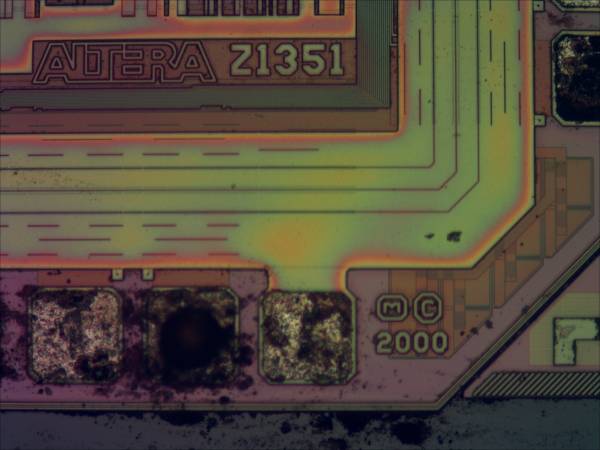

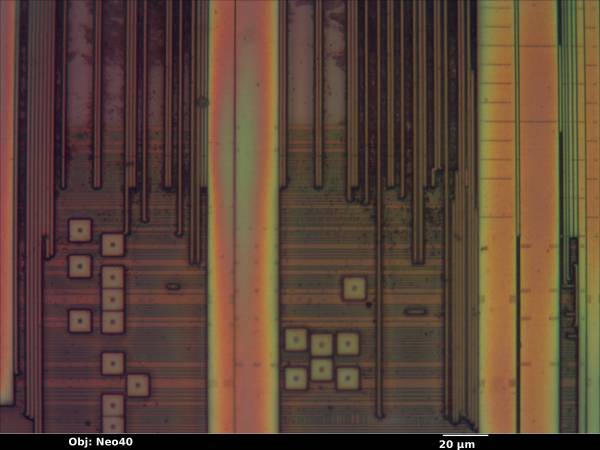

The device is heavily loaded with test points.

Global interconnect (PIA) appears to consist of pairs of vertical (power?) lines, then five signal nets between them. There are four large blocks each of four smaller blocks, each with five wires for a total of 16*5 = 80 nets. There are 66 I/O pins and 64 macrocell flipflops for a total of 130 nets so there's clearly more going on here. Even if the longer wires are counted there's only 112.

Unlike CoolRunner-II, the power rings are connected to their respective pins by fat traces on metal 4, making it easy to see which ring is which.