# **Construction Analysis**

# Advanced Micro Devices 200MHz K6 Microprocessor

# **INDEX TO TEXT**

| TITLE                  | PAGE  |

|------------------------|-------|

| INTRODUCTION           | 1     |

| MAJOR FINDINGS         | 1     |

| TECHNOLOGY DESCRIPTION |       |

| Assembly               | 2     |

| Die Process            | 2 - 3 |

| ANALYSIS RESULTS I     |       |

| Assembly               | 4     |

| ANALYSIS RESULTS II    |       |

| Die Process and Design | 5 - 7 |

| ANALYSIS PROCEDURE     | 8     |

| TABLES                 |       |

| Overall Evaluation     | 9     |

| Package Markings       | 10    |

| Package Materials      | 10    |

| Die Material Analysis  | 11    |

| Horizontal Dimensions  | 12    |

| Vertical Dimensions    | 13    |

# **INTRODUCTION**

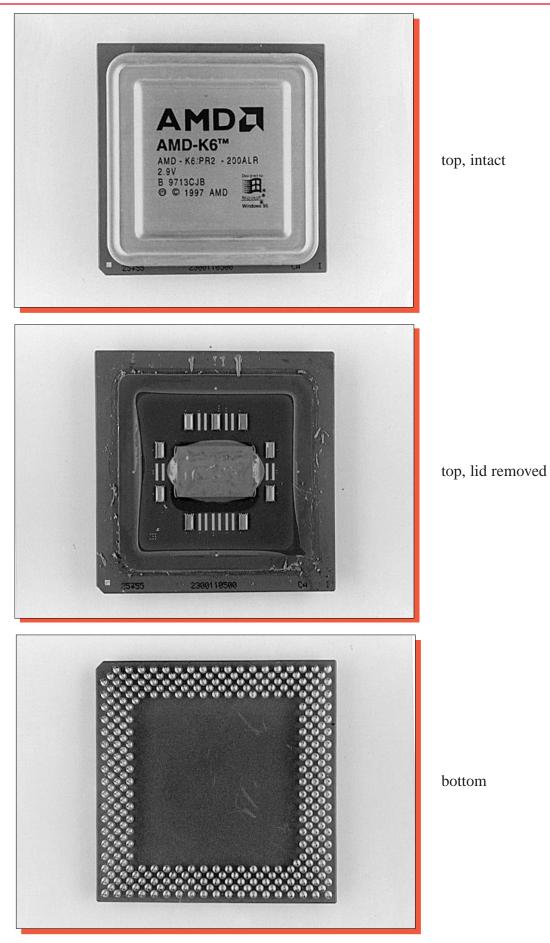

This report describes a construction analysis of the AMD 200MHz K6 Microprocessor with MMX technology. Two samples were used for the analysis. The devices were received in 321-pin CPGA packages date coded 9713.

### **MAJOR FINDINGS**

Questionable Items:<sup>1</sup> None.

#### **Special Features:**

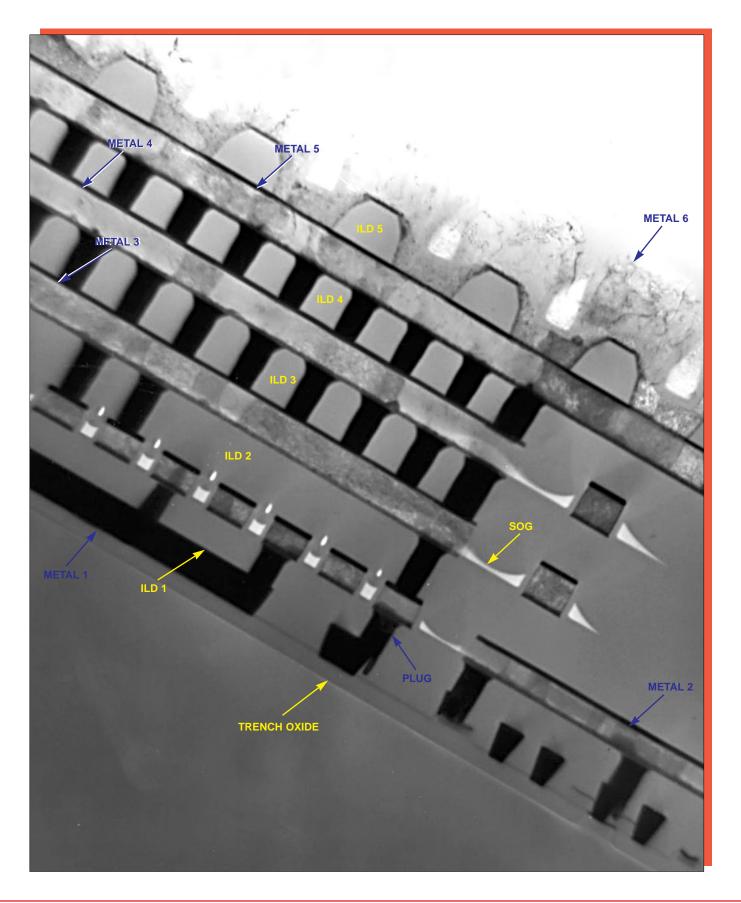

- Six metal, N-epi, CMOS process.

- Metal 1 (tungsten) was defined by a damascene process. Stacked vias were employed.

- Chemical-mechanical-planarization (CMP).

- Oxide-filled shallow-trench isolation.

- Titanium silicided diffusion structures.

<sup>1</sup>*These items present possible quality or reliability concerns. They should be discussed with the manufacturer to determine their possible impact on the intended application.*

# **TECHNOLOGY DESCRIPTION**

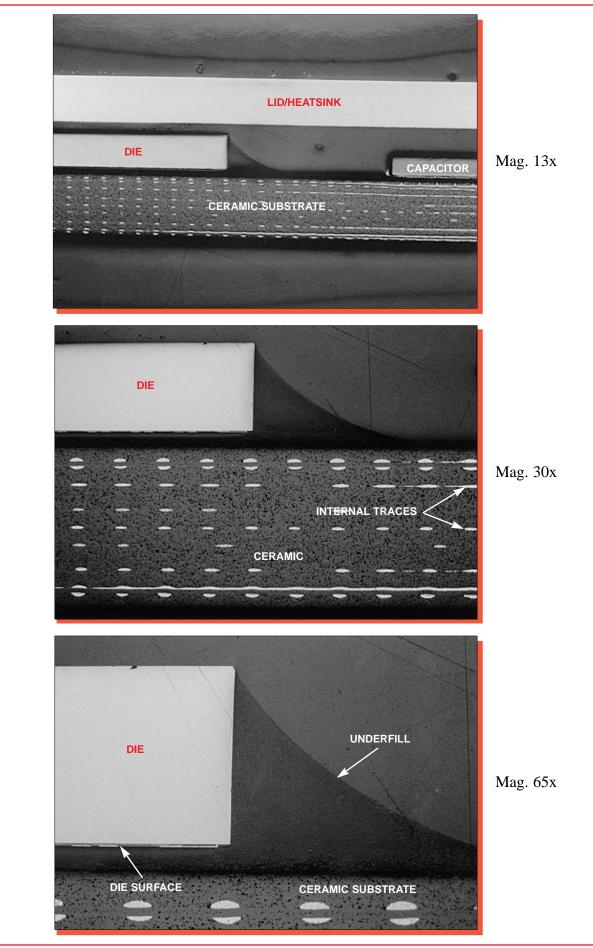

#### Assembly:

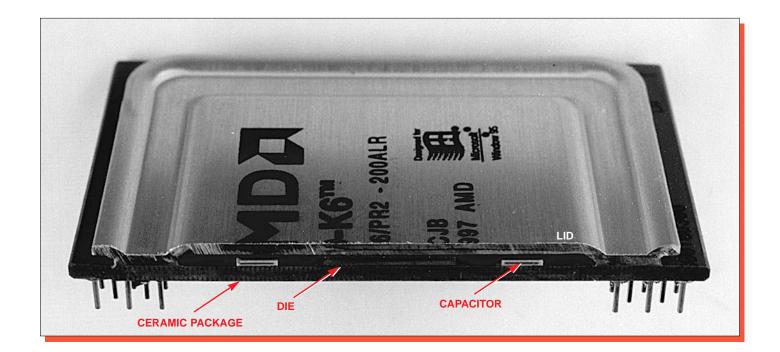

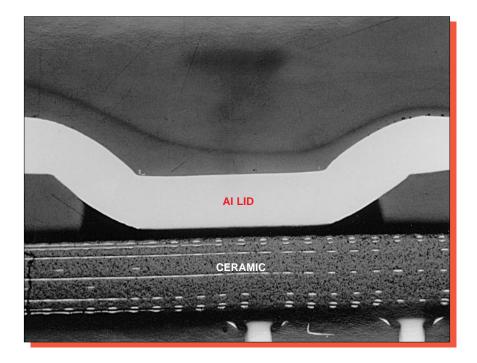

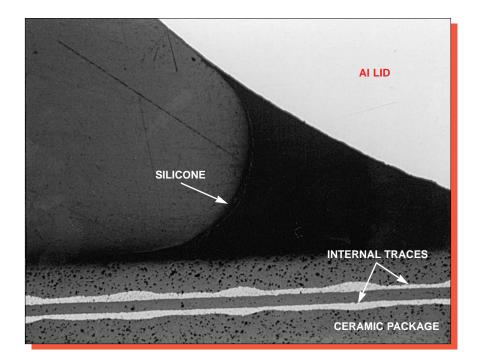

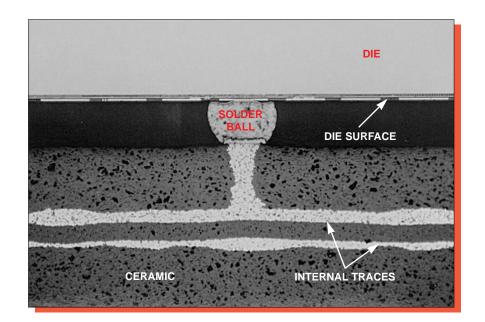

- The devices were packaged in 321-pin ceramic pin grid arrays (CPGA). An aluminum lid was employed on the top of the package. The die was mounted surface down on the ceramic substrate (C4 flip-chip assembly). The package contained nine internal levels of interconnect.

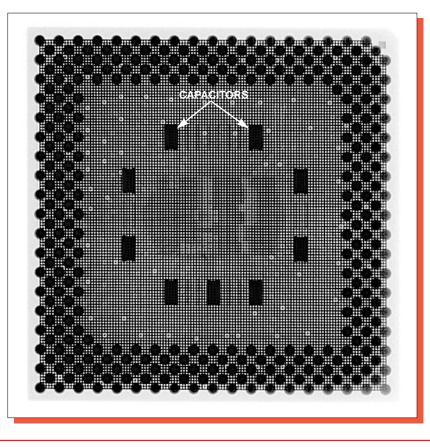

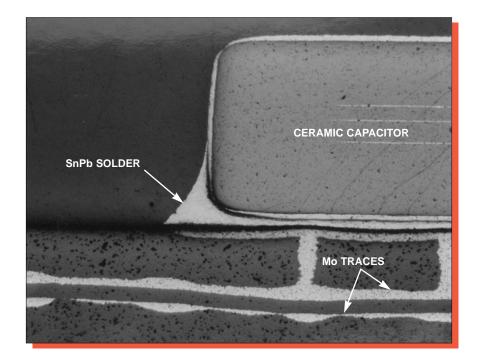

- Nine decoupling capacitors were present on top of the ceramic (inside the package).

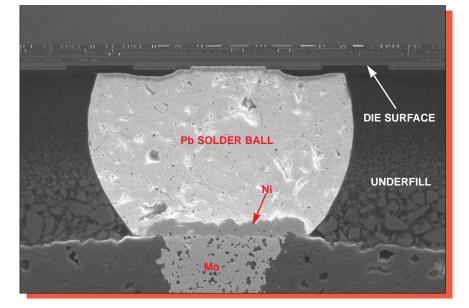

- A blue colored underfill was present between the die surface and the ceramic substrate. A gray heat conductive grease was employed between the backside of the die and the metal lid.

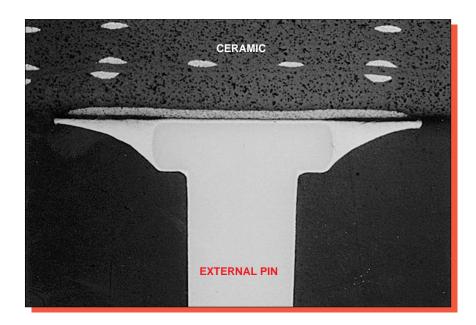

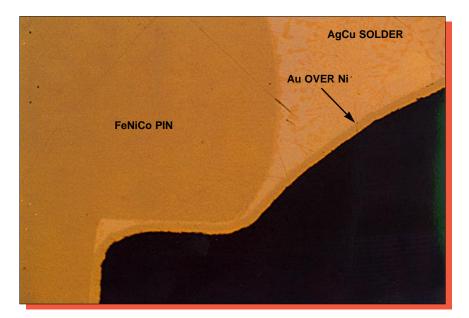

- External pins were plated with gold over nickel and were brazed to the package.

- Solder balls were employed for all connections to die metallization (C4 flip-chip process).

- Sawn dicing (full depth).

#### **Die Process:**

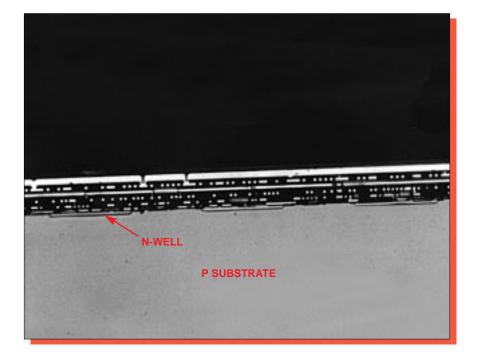

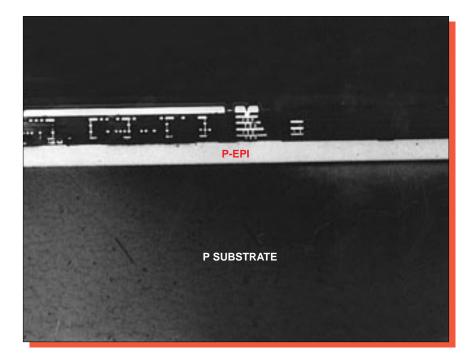

- Fabrication process: Oxide-filled shallow-trench isolation, CMOS process employing twin wells in an apparent N-epi on an N substrate.

- Die coat: A thin patterned polyimide die coat was present over the entire die.

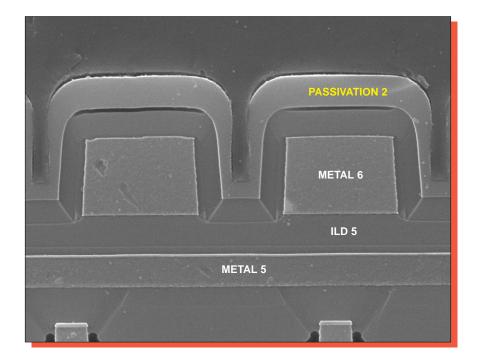

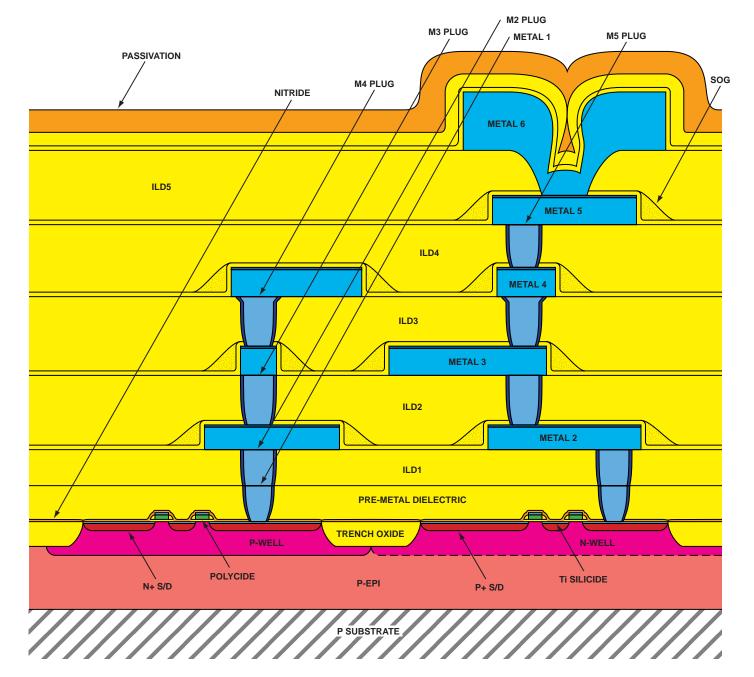

- Final passivation: A layer of nitride over two layers of glass.

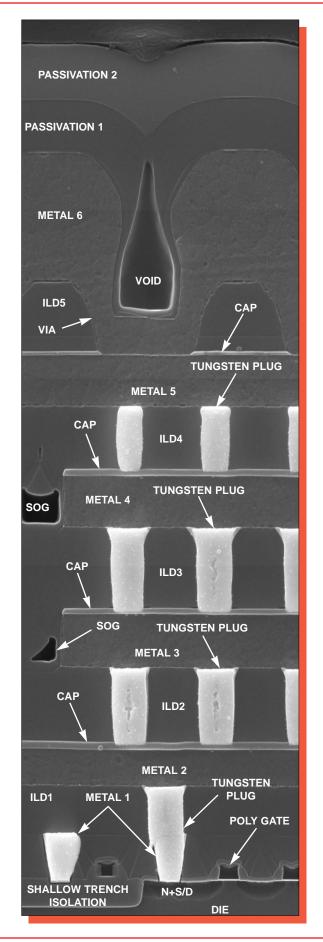

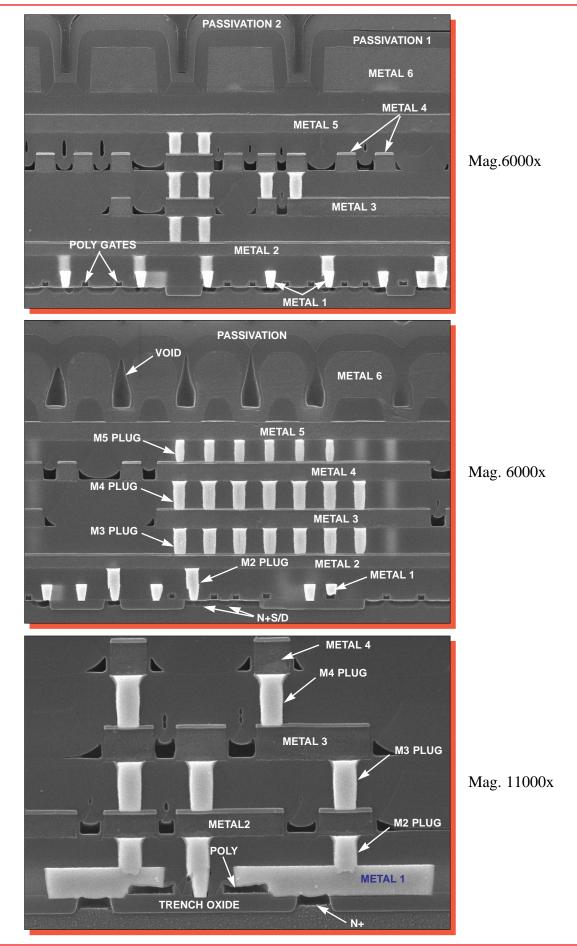

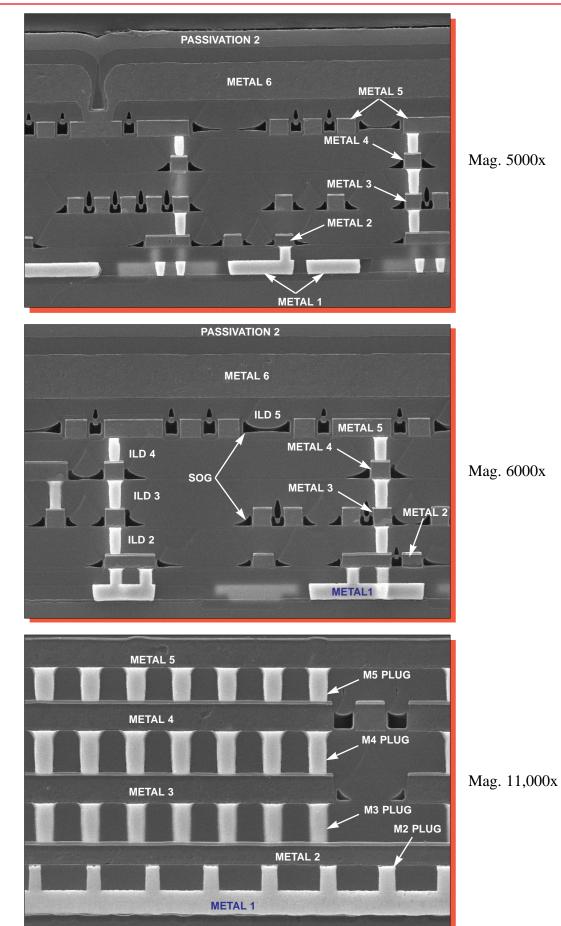

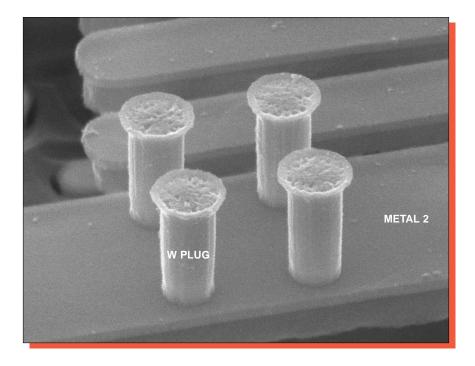

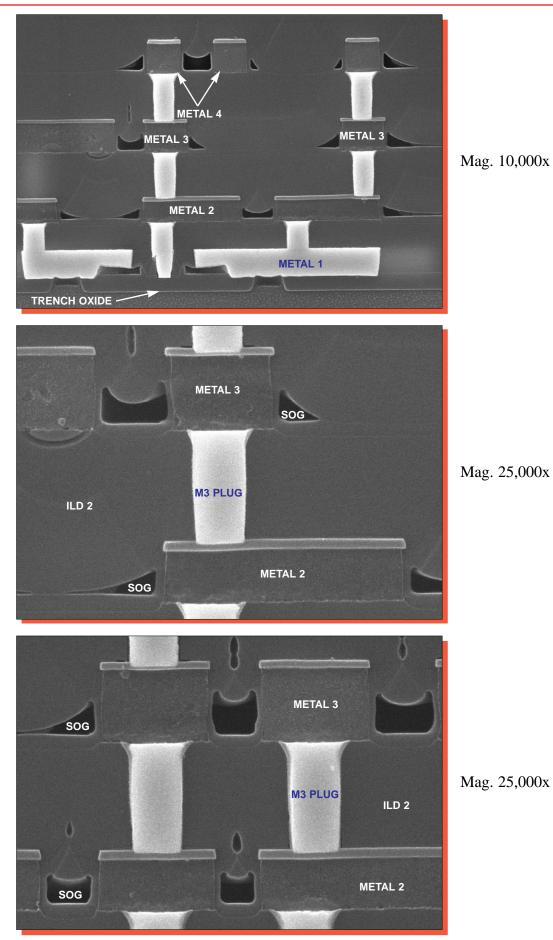

- Metallization: Six levels of metal defined by dry-etch techniques (except M1).

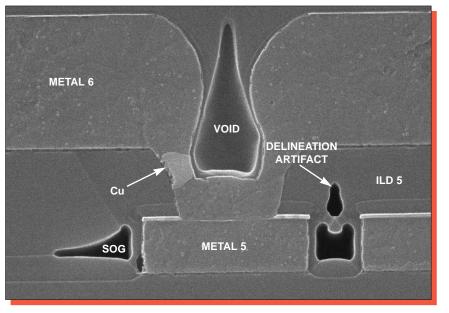

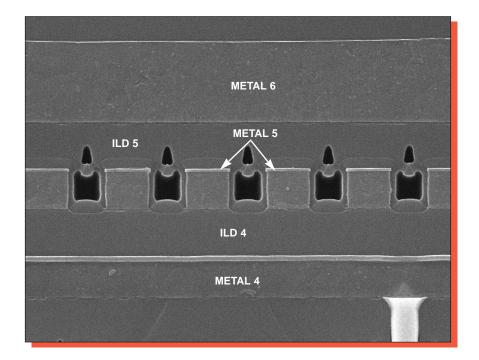

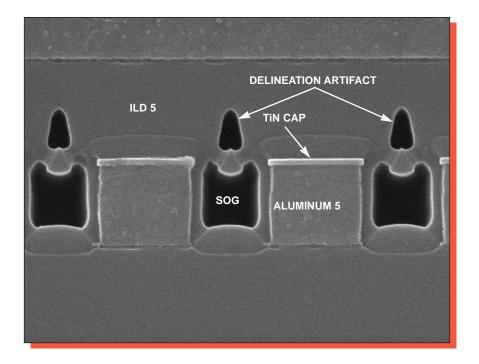

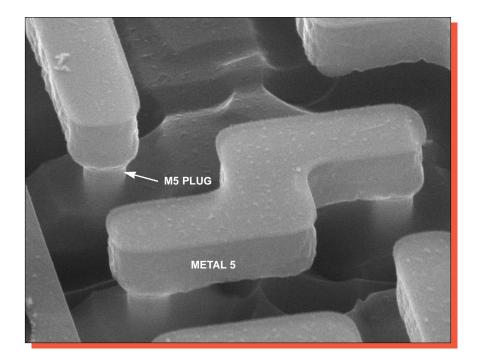

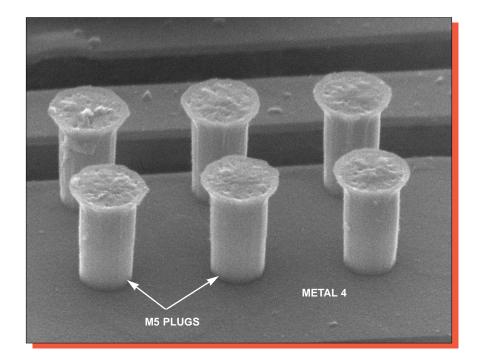

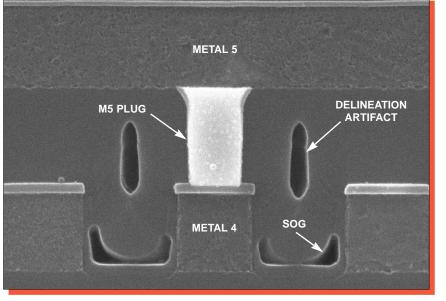

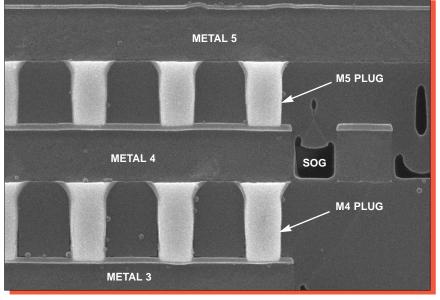

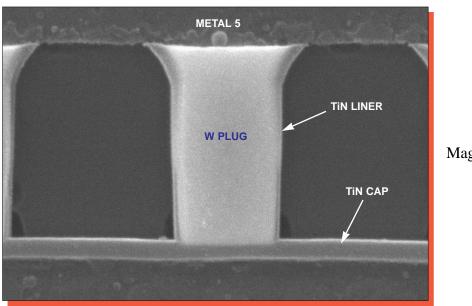

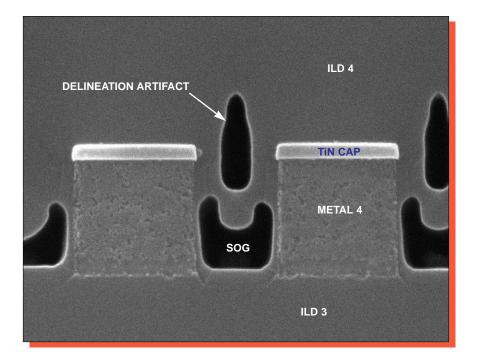

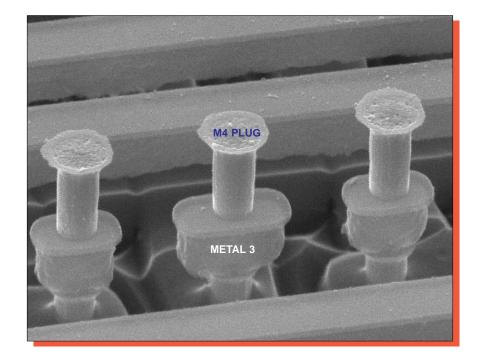

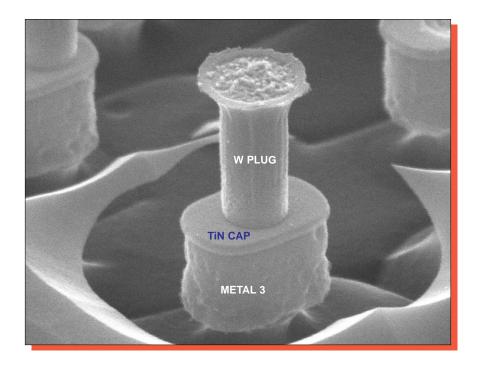

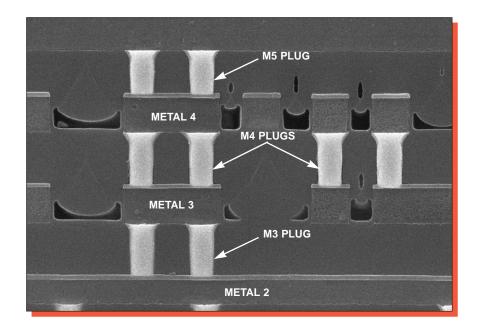

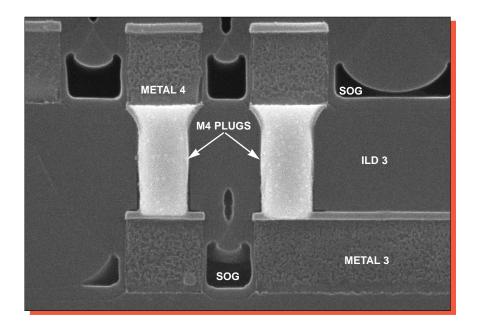

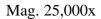

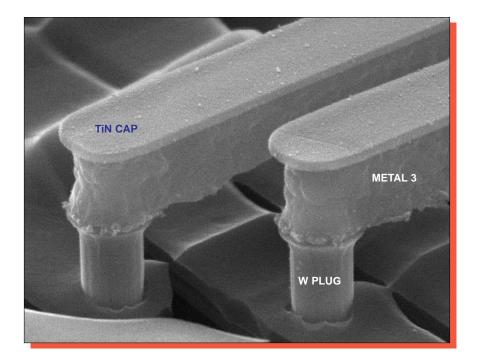

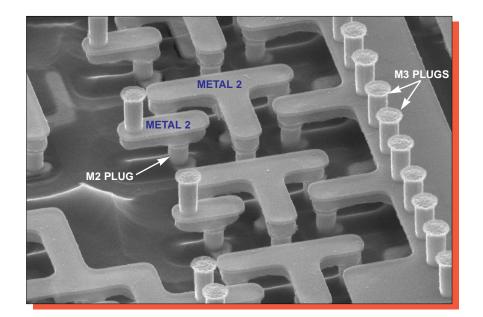

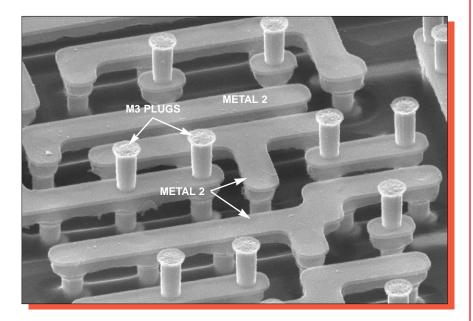

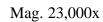

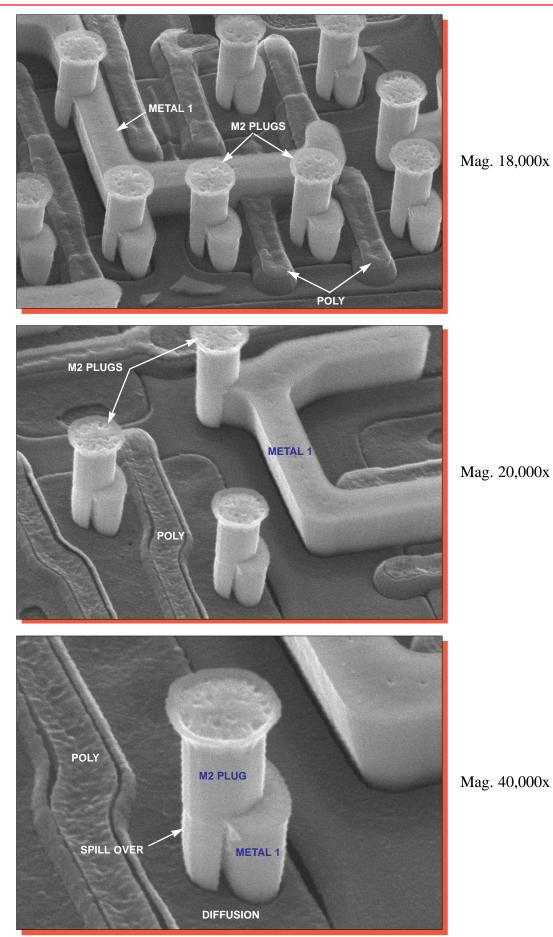

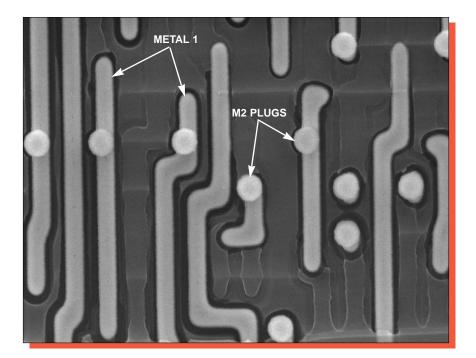

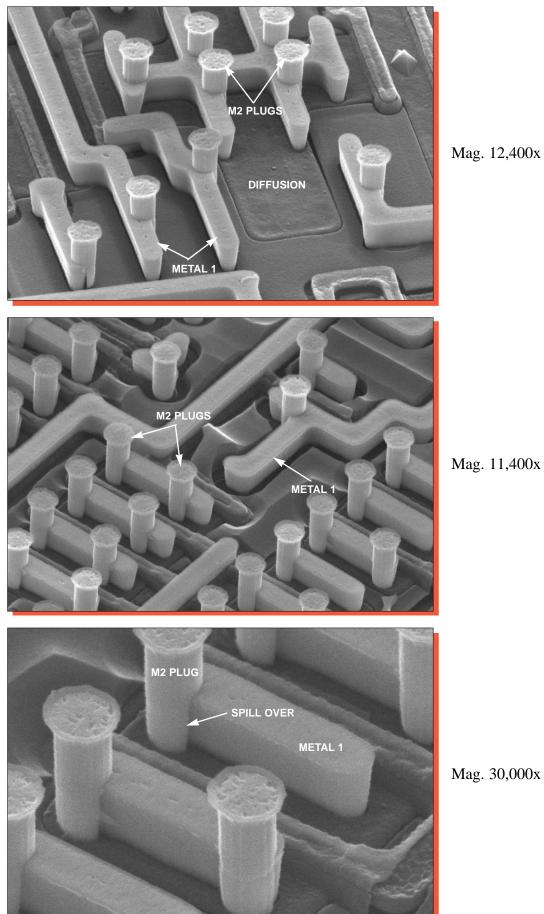

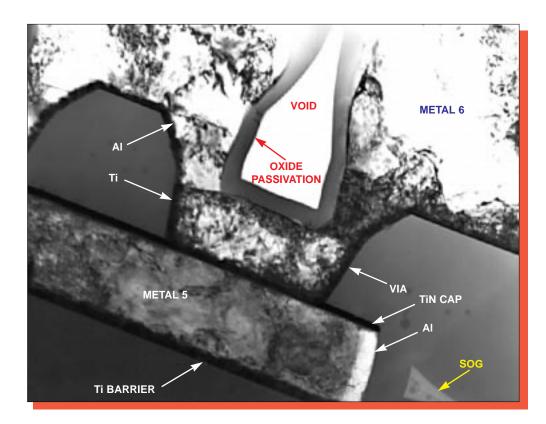

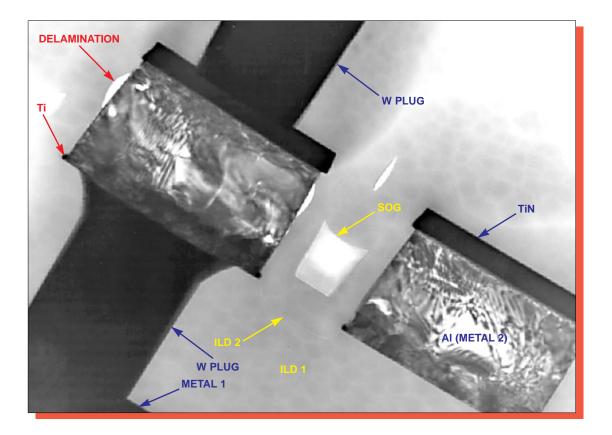

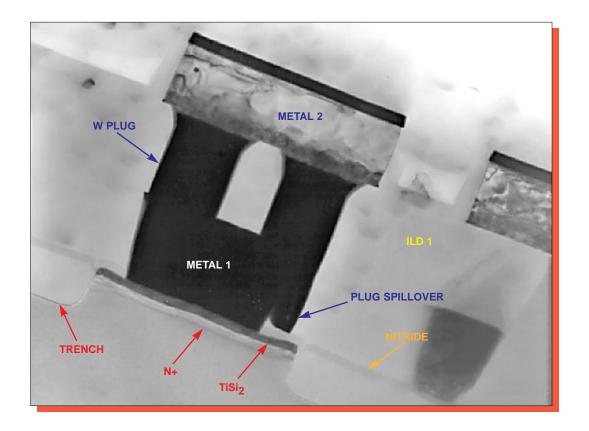

Metal 1 (tungsten) was defined by a damascene process. Metals 2 6 consisted of copper-doped aluminum. Metal 6 appeared to employ a very thin aluminum-oxide cap. Metals 2 5 employed titanium-nitride caps. There appeared to be evidence of very thin titanium adhesion layers under all metals. Tungsten plugs were employed for vias under metals 2 5. Metal 6 used standard vias. All tungsten plugs and

# **TECHNOLOGY DESCRIPTION** (continued)

tungsten metal 1 were lined with titanium-nitride. Stacked vias were employed at all levels.

- Interlevel dielectrics: Interlevel dielectrics 2 5 used the same dielectric structure. A very thin glass was deposited first, followed by an SOG (spin-on-glass) followed by a thick layer of glass. The third layer of glass was planarized by CMP which left the surface very planar. No CMP was performed directly under metal 6. Interlevel dielectric 1 (between M1 and M2) consisted of a single thick layer of glass which had also been subjected to CMP.

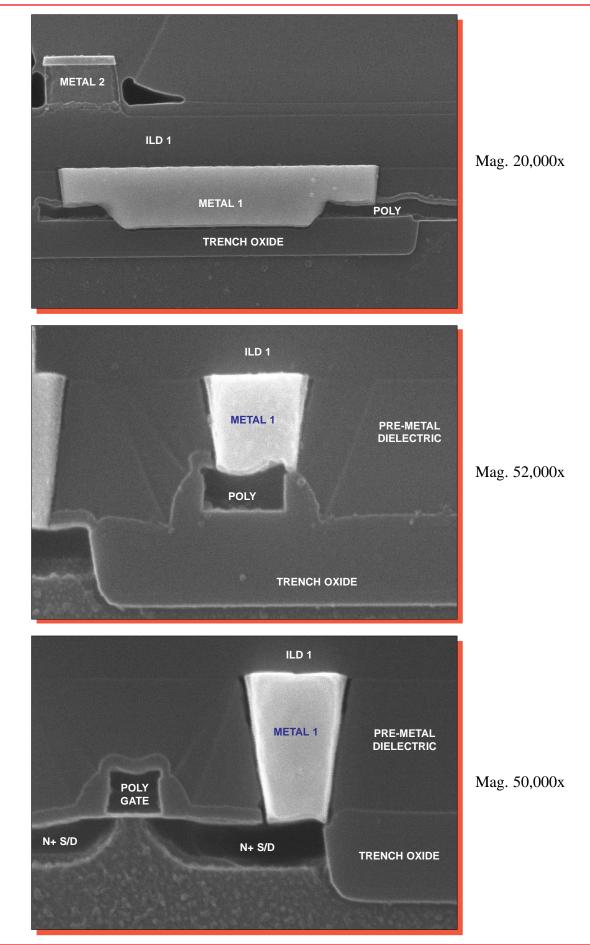

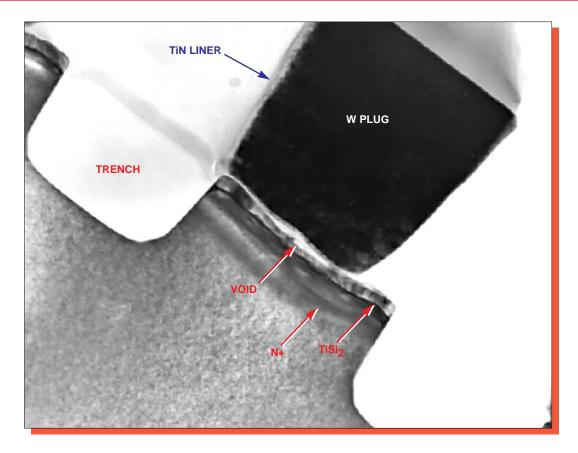

- Pre-metal glass: A thick layer of glass over a thin nitride. This dielectric was also planarized by CMP.

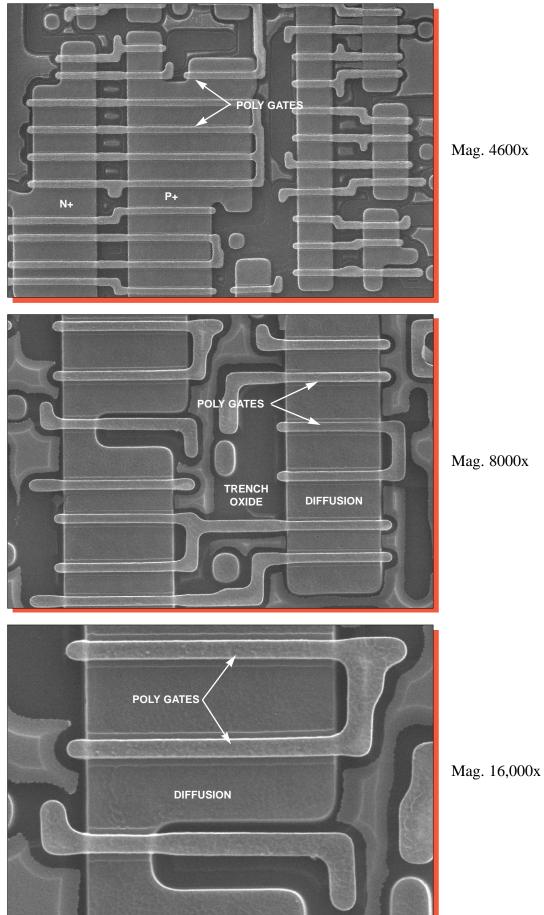

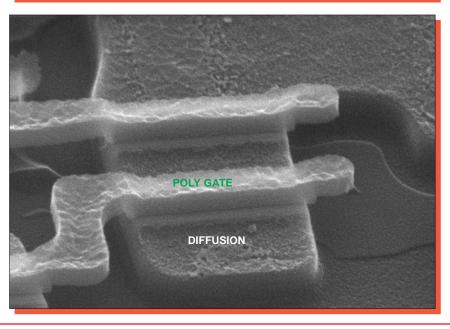

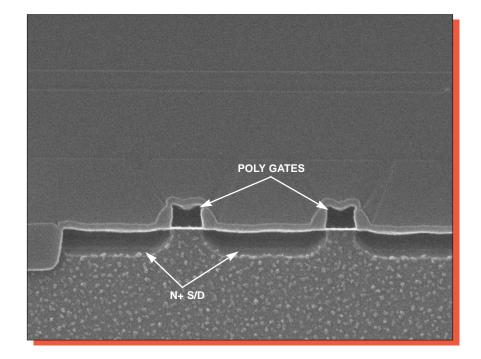

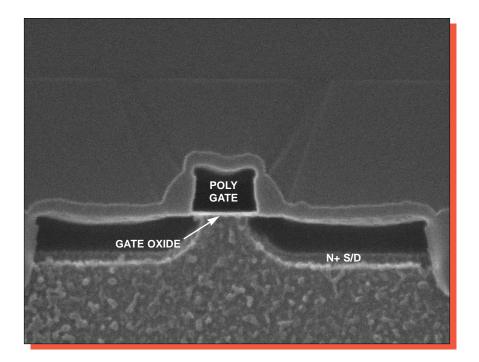

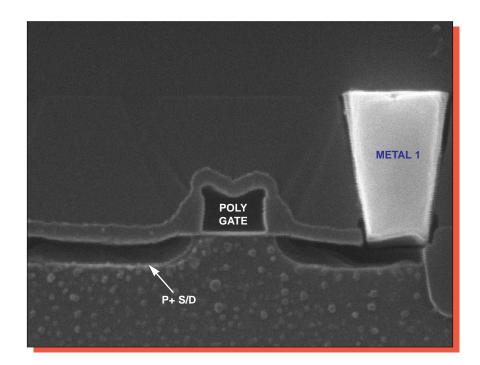

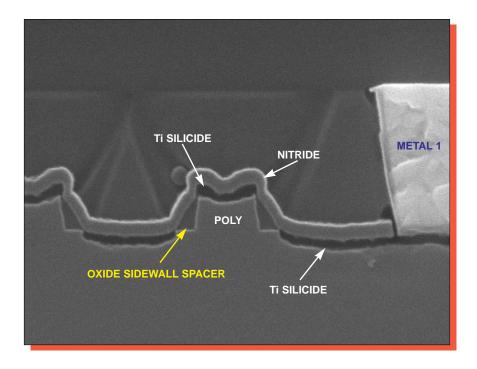

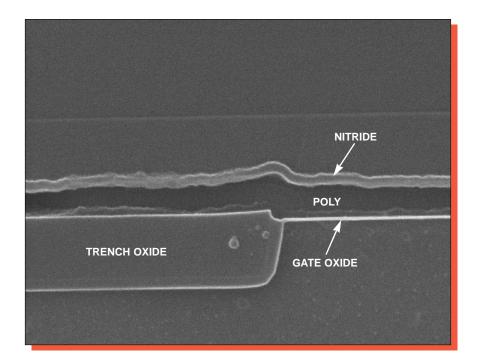

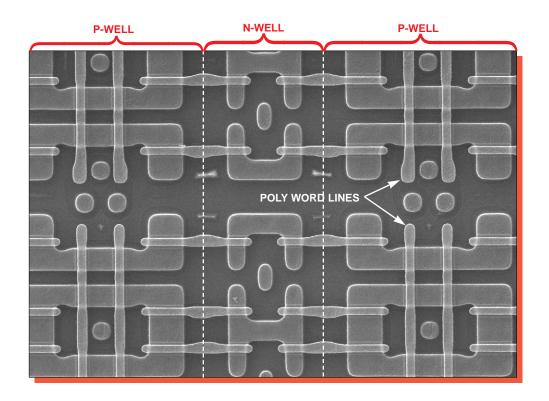

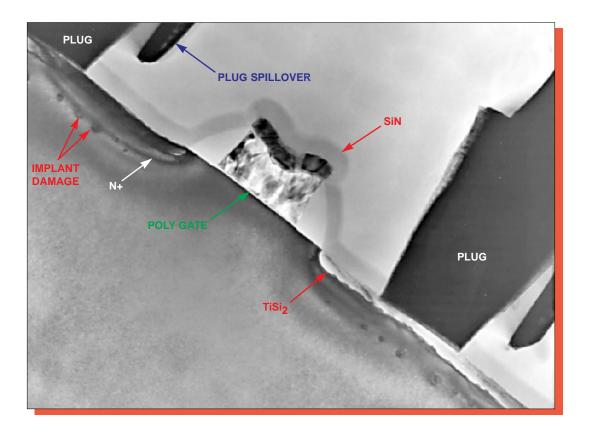

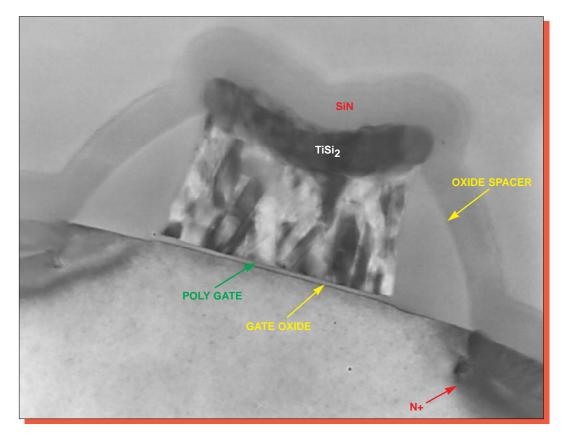

- Polysilicon: A single layer of dry-etched polycide (poly and titanium-silicide). This layer was used to form all gates on the die. Oxide sidewall spacers were used to provide the LDD spacing.

- Diffusions: Implanted N+ and P+ diffusions formed the sources/drains of transistors. Titanium was sintered into the diffusions (salicide process).

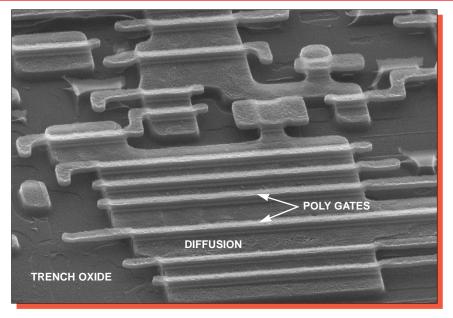

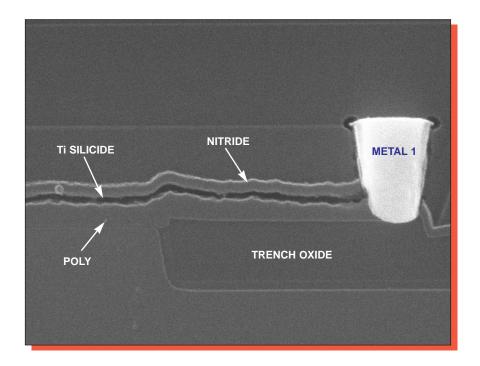

- Isolation: Field oxide isolation consisted of oxide-filled shallow-trench isolation. It was very planar with the diffused silicon surfaces.

- Wells: Twin-wells in a N-epi on a N substrate.

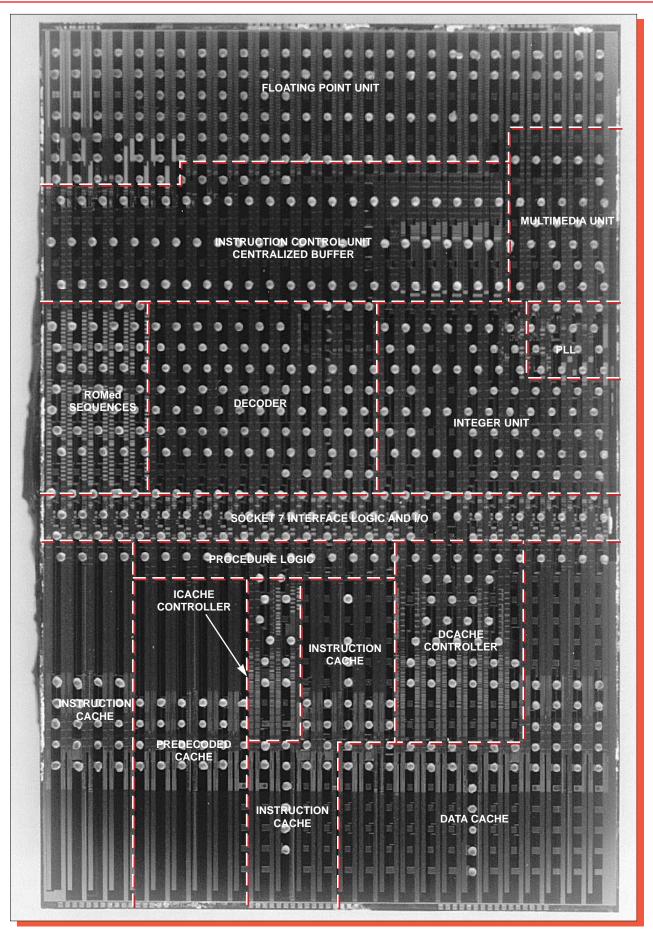

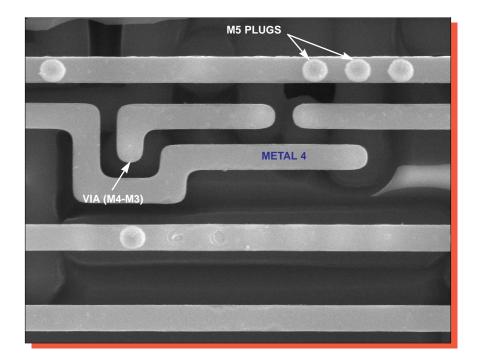

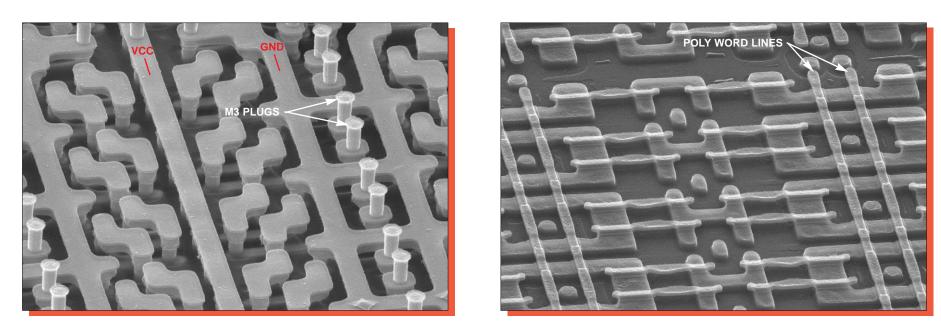

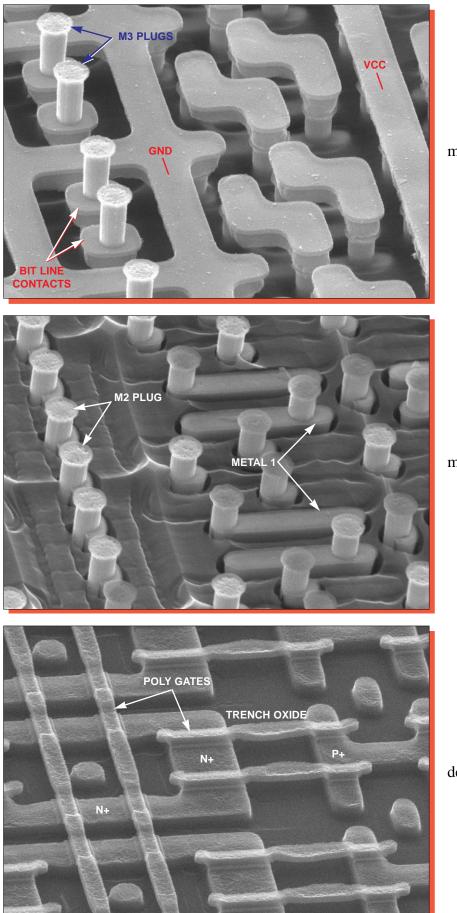

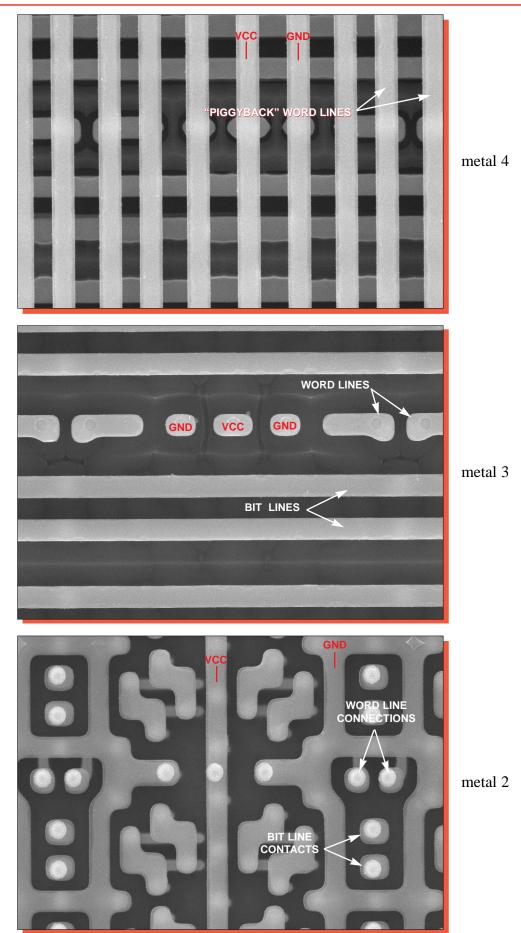

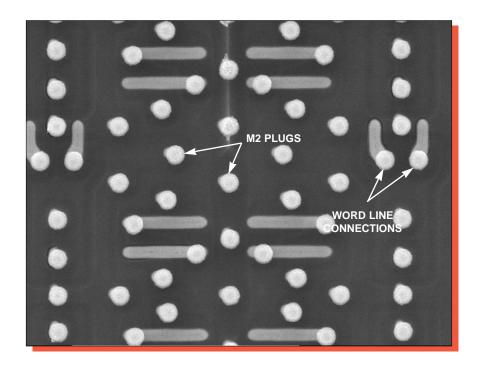

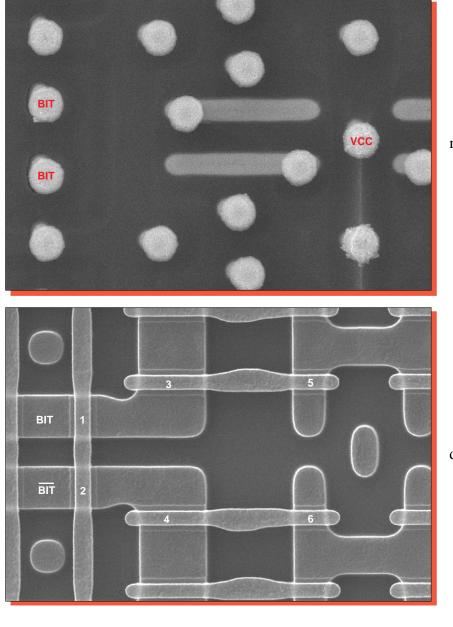

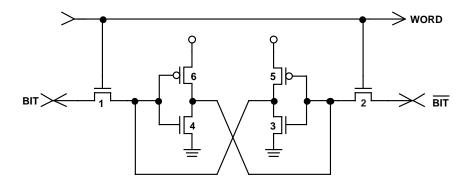

- SRAM: On-chip Level 1 data and instruction cache memory cell arrays (32KByte each) were employed. The memory cells used a 6T CMOS SRAM cell design. Metal 4 distributed Vcc and GND and formed "piggyback" word lines (via metals 1 3). Metal 3 formed the bit lines and metal 2 distributed GND and Vcc throughout the cells and was used as cell interconnect. Metal 1 also provided cell interconnect. Polycide formed the select and storage gates. Cell pitch was 4.5 x 7 microns (31.5 microns<sup>2</sup>).

- No redundancy fuses were found.

# ANALYSIS RESULTS I

## Assembly:

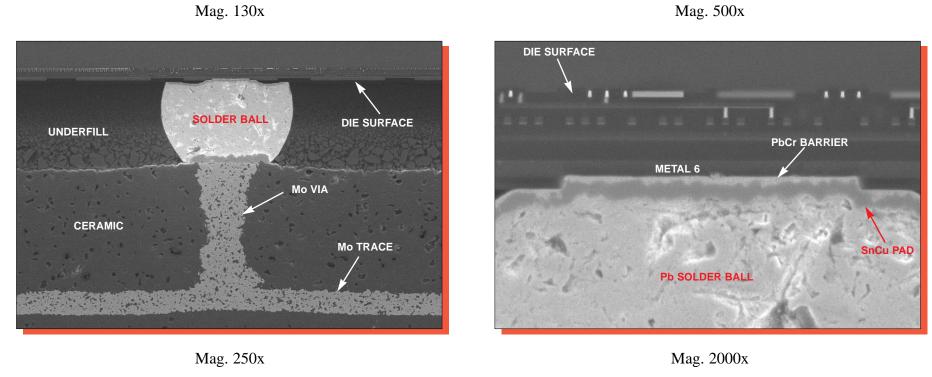

**Figures 1 - 8**

Questionable Items:<sup>1</sup> None.

### **Special Features:**

• CPGA with metal lid.

# General items:

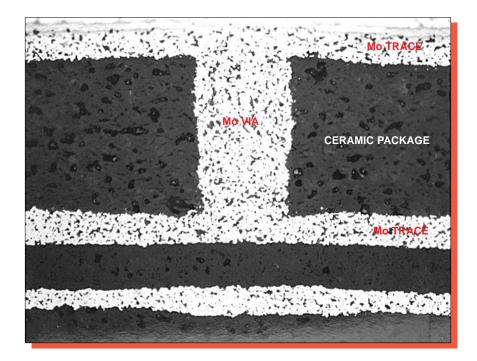

- The devices were packaged in 321-pin ceramic PGA packages. An aluminum lid/heat dissipater was employed. It was attached to the ceramic substrate with a silicone-type adhesive. The die was mounted surface down on the ceramic (flip-chip assembly). The PGA contained nine molybdenum internal interconnect levels. Vias between trace levels were also formed with molybdenum. Nine ceramic chip capacitors were present inside the package.

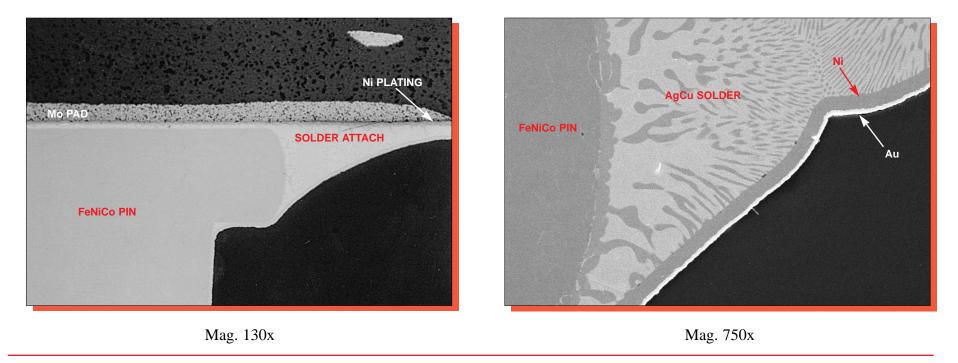

- Overall package quality: Good. No defects were found on the external or internal portions of the packages. External pins (iron-nickel-cobalt) were straight and placement was good. No voids were noted in the silver-copper solder. External plating of the pins was of good quality (gold over nickel).

- Die connections: Lead solder balls were used for connections to the die (C4 process). Ball placement was good. Die pad structure consisted of tin-copper with a lead-chromium barrier. Ball pitch was 14.5 mils (0.34mm). There were a total of 682 solder balls present on the die. A blue colored underfill was present between the die and the ceramic substrate. No voids were noted in this material. A gray heat conductive grease was used between the backside of the die and the lid for a thermal transfer.

- Die dicing: Die separation was by full depth sawing and showed normal quality workmanship. No large chips or cracks were present at the die edges.

<sup>1</sup>*These items present possible quality or reliability concerns. They should be discussed with the manufacturer to determine their possible impact on the intended application.*

# ANALYSIS RESULTS II

### **Die Process and Design:**

**Figures 9 - 52**

Questionable Items:<sup>1</sup> None.

### **Special Features:**

- Six metal, N-epi, CMOS process.

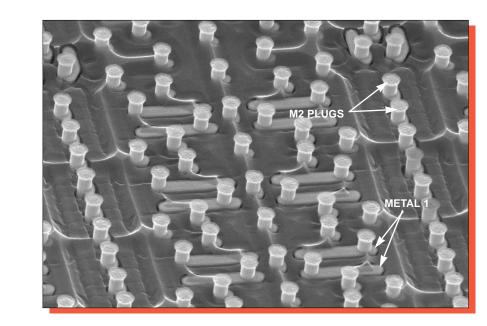

- Metal levels 2 5 employed tungsten via plugs. Metal 1 was defined by a damascene process. Stacked vias were employed at all levels.

- Chemical-mechanical-planarization (CMP).

- Oxide-filled shallow-trench isolation.

- Titanium silicided diffusion structures.

# **General Items:**

- Fabrication process: Oxide-filled shallow-trench isolation, CMOS process employing twin-wells in an apparent N-epi on an N substrate. No problems were found in the process.

- Design implementation: Die layout was clean and efficient. Alignment was good at all levels.

- Surface defects: No toolmarks, masking defects, or contamination areas were found.

- Die coat: A patterned polyimide die coat was present over the entire die surface.

<sup>1</sup>*These items present possible quality or reliability concerns. They should be discussed with the manufacturer to determine their possible impact on the intended application.*

## ANALYSIS RESULTS II (continued)

- Final passivation: A layer of nitride over two layers of glass. Coverage was good. Edge seal was also good as the passivation extended to the scribe lane to seal the metallization.

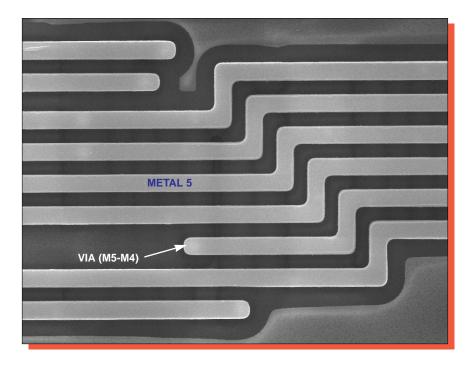

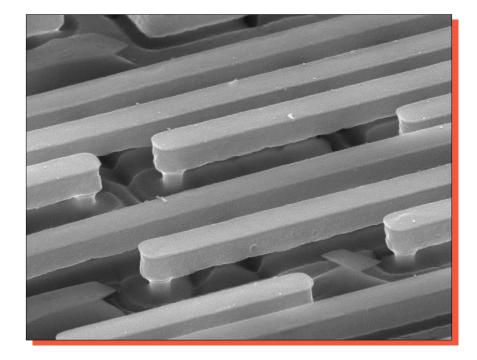

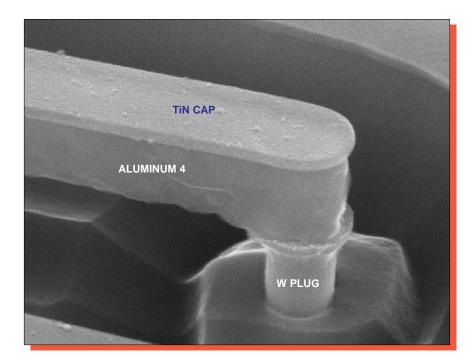

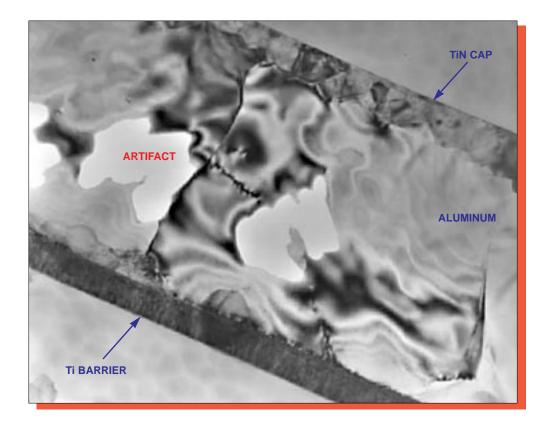

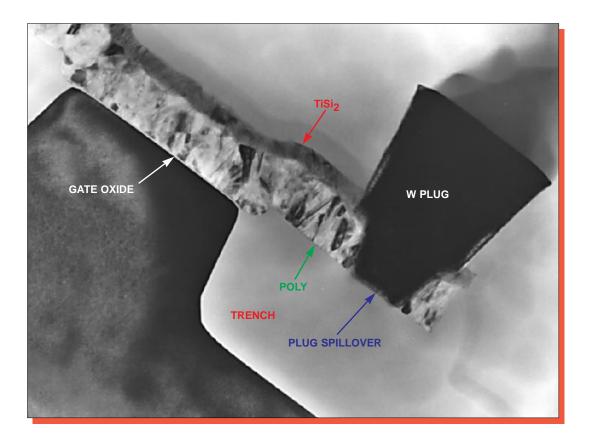

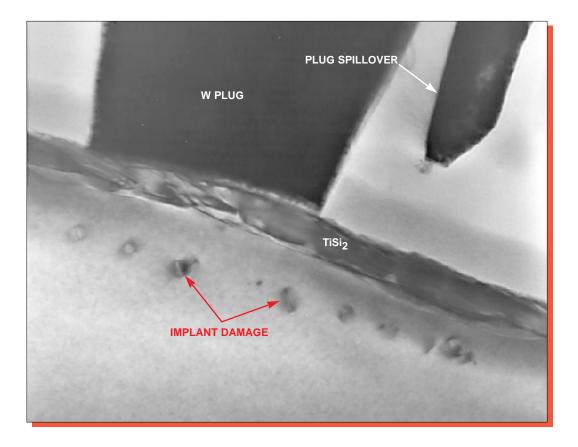

- Metallization: Six levels of metal interconnect. Metals 2 6 consisted of copperdoped aluminum. Metals 2 - 5 employed titanium-nitride caps. Metal 6 apparently employed a thin aluminum-oxide cap. There appeared to be evidence of very thin titanium adhesion layers under all metals. Tungsten plugs were employed with metals 2 - 5. Standard vias were employed under metal 6. All plugs were lined with titanium-nitride underneath and the presumed adhesion layer over top. Metal 1 consisted of tungsten defined by a damascene process. The metal 1 tungsten was also lined with titanium-nitride and an apparent titanium adhesion layer.

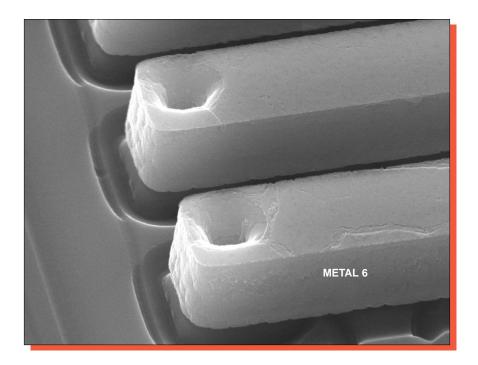

- Metal patterning: All aluminum metal levels were defined by a dry etch of good quality. Metal lines were not widened at via connections.

- Metal defects: None. No voiding, notching or cracking of the metal layers was found. No silicon nodules were found following removal of the metal layers.

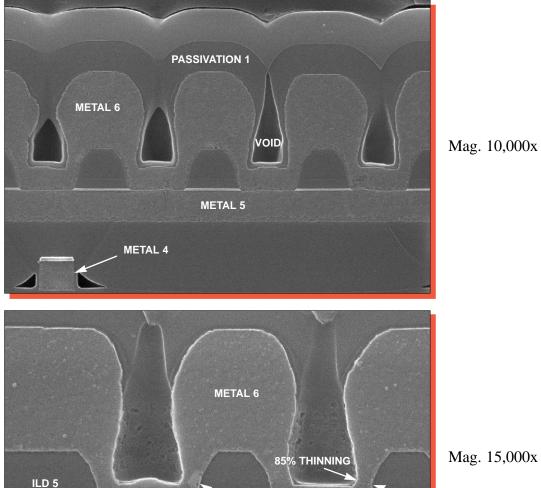

- Metal step coverage: Metal 6 thinned up to 85 percent at vias. Although the thinning exceeds MIL-STDs (70 percent) it is not considered a serious reliability concern. No metal thinning was present at the connections to the tungsten via plugs or metal 1. The absence of thinning is due to the good control of plug height and the planarization technique employed.

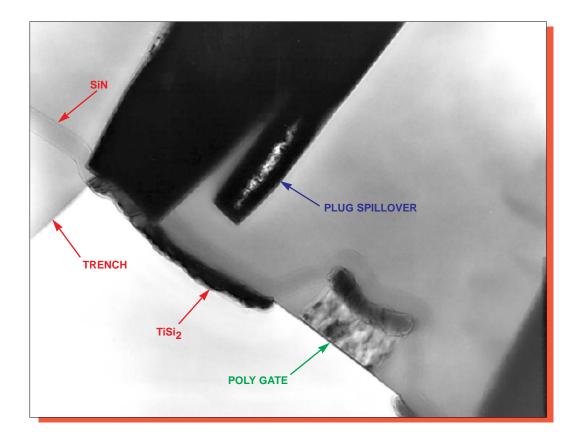

- Vias and contacts: All via and contact cuts were defined by a dry etch of good quality. Again, alignment of the metals and plugs was good. Metal 2 tungsten plugs "spilled over" one edge of the tungsten metal 1. IBM uses this "borderless" contact technique for improved contact resistance. Vias and contacts were placed directly over one another (stacked vias). No problems were noted.

- Interlevel dielectrics: Interlevel dielectrics 2 5 consisted of the same type of oxide structure. A very thin glass was deposited first, followed by an SOG and a thick layer of glass. The thick layer of glass was subjected to CMP which left the surface very planar. No CMP was performed on ILD 5 (under metal 6). Interlevel

# ANALYSIS RESULTS II (continued)

dielectric 1 consisted of a single thick layer of glass which had also been subjected to CMP. No problems were found with any to these layers.

- Pre-metal glass: A thick layer of silicon-dioxide over a thin nitride. This layer was also planarized by chemical-mechanical-planarization. No problems were found.

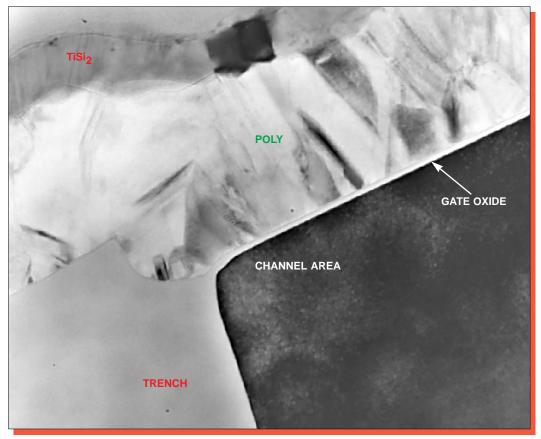

- Polysilicon: A single level of polycide (poly and titanium-silicide) was used. It formed all gates and word lines in the array. Definition was by dry etch of good quality. Oxide sidewall spacers were used throughout and left in place. No problems were found.

- Isolation: The device used oxide-filled shallow-trench isolation which was quite planar with the silicon surface. No problems were present.

- Diffusions: Implanted N+ and P+ diffusions were used for sources and drains. Titanium was sintered into the diffusions (salicide process) to reduce series resistance. An LDD process was used employing oxide sidewall spacers. No problems were found.

- Wells: Twin-wells were used in what we believe to be an N-epi on an N substrate. Definition was normal.

- Buried contacts: Direct poly to diffusion contacts were not used.

- SRAM: As mentioned, on-chip Level 1 data and instruction cache memory cell arrays (32KByte each) were employed on the device. The SRAM cell array used a 6T CMOS SRAM cell design. Metal 4 distributed Vcc and GND and formed "piggyback" word lines (via metals 1 3). Metal 3 formed the bit lines. Metal 2 distributed GND and Vcc throughout the cells and was used as cell interconnect. Metal 1 also provided cell interconnect. Polycide formed the word lines/select and storage gates. Cell pitch was 4.5 x 7 microns (31.5 microns<sup>2</sup>).

- No redundancy fuses were noted.

#### **PROCEDURE**

The devices were subjected to the following analysis procedures:

External inspection X-ray Package section and EDX Die optical inspection Delayer to metal 6 and inspect Aluminum removal (metal 6) Delayer to metal 5 and inspect Aluminum removal (metal 5) and inspect tungsten plugs Delayer to metal 4 and inspect Aluminum removal (metal 4) and inspect tungsten plugs Delayer to metal 3 and inspect Aluminum removal (metal 3) and inspect tungsten plugs Delayer to metal 2 and inspect Aluminum removal (metal 2) and inspect tungsten plugs Delayer to metal 1 and inspect Tungsten removal (metal 1) Delayer to polycide/substrate and inspect Die sectioning (90° for SEM) Measure horizontal dimensions Measure vertical dimensions Die material analysis

# **OVERALL QUALITY EVALUATION:** Overall Rating: Normal to Good.

# **DETAIL OF EVALUATION**

| Package integrity                | G                                     |

|----------------------------------|---------------------------------------|

| Package markings                 | G                                     |

| Die placement                    | G                                     |

| Solder ball placement            | G                                     |

| Solder ball interconnect quality | G                                     |

| Dicing quality                   | Ν                                     |

| Die attach quality               | G                                     |

| Die attach method                | C4 solder ball interconnect technique |

| Dicing method                    | Sawn                                  |

Die surface integrity:

| Toolmarks (absence)       | G |

|---------------------------|---|

| Particles (absence)       | G |

| Contamination (absence)   | G |

| Process defects (absence) | G |

| General workmanship       | G |

| Passivation integrity     | G |

| Metal definition          | G |

| Metal integrity           | Ν |

| Metal registration        | G |

| Contact coverage          | G |

| Via/contact registration  | Ν |

| Etch control (depth)      | Ν |

*G* = *Good*, *P* = *Poor*, *N* = *Normal*, *NP* = *Normal/Poor*

# PACKAGE MARKINGS

# <u>TOP (lid)</u>

AMD (logo) AMD-K6™ AMD-K6/PR2-200ALR 2.9V B9713CJB © 1997 AMD Designed for Microsoft® Windows® 95 (logo)

# PACKAGE MATERIALS

| Lid:                        | Aluminum (Al)               |

|-----------------------------|-----------------------------|

| Lid attach:                 | Silicone-type adhesive      |

| External pins:              | Iron-nickel-cobalt (FeNiCo) |

| Pin plating:                | Gold over nickel (Au/Ni)    |

| Pin attach:                 | Silver-copper (AgCu) solder |

| Contact pads:               | Nickel (Ni)                 |

| Internal traces and vias:   | Molybdenum (Mo)             |

| Solder balls:               | Lead (Pb)                   |

| Bond pads:                  | Tin-copper (SnCu)           |

| Bond pad barrier:           | Lead-chromium (PbCr)        |

| Capacitor end terminations: | Silver (Ag)                 |

| End termination barrier:    | Nickel (Ni)                 |

| Capacitor attach            | Tin-lead (SnPb) solder      |

# **DIE MATERIAL ANALYSIS**

| Final passivation:            | Single layer of nitride over dual glass layers.                                                   |

|-------------------------------|---------------------------------------------------------------------------------------------------|

| Metallization 6:              | Aluminum with an aluminum-oxide cap (and a thin titanium adhesion layer?).                        |

| Metallization 2 - 5:          | Aluminum with titanium-nitride caps (and thin adhesion layers?).                                  |

| Interlevel dielectrics 2 - 5: | A thin layer of glass followed by an SOG and a thick layer of glass.                              |

| Interlevel dielectric 1:      | Thick layer of glass.                                                                             |

| Metallization 1:              | Tungsten (damascene process) with titanium-nitride liner and an apparent titanium adhesion layer. |

| Vias (M2 - M5):               | Tungsten (lined with titanium-nitride).                                                           |

| Pre-metal glass:              | Thick layer of silicon-dioxide over a thin nitride.                                               |

| Polycide:                     | Titanium-silicide on polysilicon.                                                                 |

| Salicide on diffusions:       | Titanium-silicide.                                                                                |

# HORIZONTAL DIMENSIONS

| Die size:                       | 10.3 x 15.6 mm (405 x 616 mils)                  |

|---------------------------------|--------------------------------------------------|

| Die area:                       | 161 mm <sup>2</sup> (249,480 mils <sup>2</sup> ) |

| Min pad size:                   | 0.1 x 0.1 mm (4 x 4 mils)                        |

| Min pad window:                 | 0.05 mm (1.9 mil octagon)                        |

| Min pad space:                  | 0.27 mm (10.5 mils)                              |

| Min metal 6 width:              | 3 microns                                        |

| Min metal 6 space:              | 2.3 microns                                      |

| Min metal 5 width:              | 0.9 micron                                       |

| Min metal 5 space:              | 0.8 micron                                       |

| Min metal 4 width:              | 0.75 micron                                      |

| Min metal 4 space:              | 0.5 micron                                       |

| Min metal 3 width:              | 0.75 micron                                      |

| Min metal 3 space:              | 0.5 micron                                       |

| Min metal 2 width:              | 0.9 micron                                       |

| Min metal 2 space:              | 0.5 micron                                       |

| Min metal 1 width:              | 0.45 micron                                      |

| Min metal 1 space:              | 0.45 micron                                      |

| Min via (M6-to-M5):             | 1.4 micron                                       |

| Min via (M5-to-M4):             | 0.55 micron                                      |

| Min via (M4-to-M3):             | 0.55 micron                                      |

| Min via (M3-to-M2):             | 0.55 micron                                      |

| Min via (M2-to-M1):             | 0.6 micron                                       |

| Min contact:                    | 0.4 micron                                       |

| Min polycide width:             | 0.32 micron                                      |

| Min polycide space:             | 0.65 micron                                      |

| Min gate length* - (N-channel): | 0.32 micron                                      |

| - (P-channel):                  | 0.32 micron                                      |

| SRAM cell size:                 | 31.5 microns <sup>2</sup>                        |

| SRAM cell pitch:                | 4.5 x 7 microns                                  |

\*Physical gate length

#### **VERTICAL DIMENSIONS**

#### Die thickness:

#### 0.7 mm (28 mils)

#### Layers:

**Passivation 2**: 0.8 micron Passivation 1 (both glass layers): 0.8 micron Metal 6: 2.1 microns 0.9 micron Interlevel dielectric 5 - glass 2: - glass 1 0.2 micron Metal 5 - cap: 0.06 micron (approximate) - aluminum: 0.8 micron 1.0 micron - plugs: Interlevel dielectric 4 - glass 2: 0.9 - 1.7 micron - glass 1: 0.1 micron 0.1 micron Metal 4 - cap: 0.75 micron - aluminum: 1.2 micron - plugs: Interlevel dielectric 3 - glass 2: 1.1 - 1.9 micron 0.08 micron (approximate) - glass 1: Metal 3 - cap: 0.1 micron 0.8 micron - aluminum: - plugs: 1.2 micron Interlevel dielectric 2 - glass 2: 1.1 - 1.7 micron - glass 1: 0.1 micron 0.1 micron Metal 2 - cap: - aluminum: 0.6 micron 0.7 micron - plugs: Interlevel dielectric 1: 0.7 micron 0.45 - 0.7 micron Metal 1: Nitride layer: 0.1 micron Pre-metal glass: 0.6 micron Polycide - silicide: 0.05 micron (approximate) - poly: 0.15 micron Trench oxide: 0.45 micron N+S/D: 0.15 micron P+S/D: 0.13 micron P-well: 1.5 micron (approximate) 7 microns N-epi:

# **INDEX TO FIGURES**

| ASSEMBLY                       | Figures 1 - 8   |

|--------------------------------|-----------------|

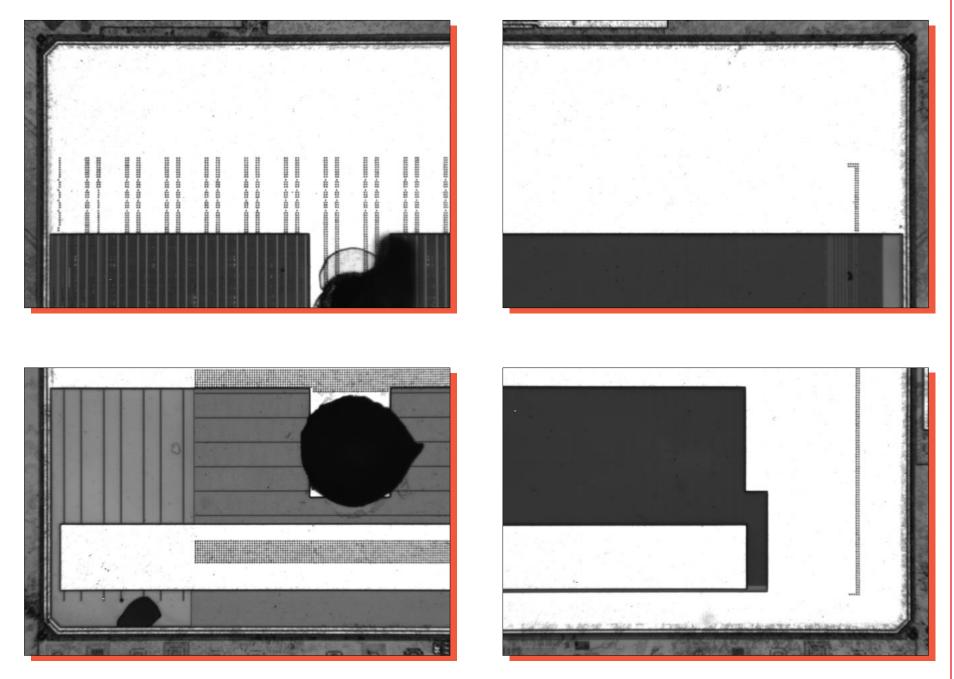

| DIE LAYOUT AND IDENTIFICATION  | Figures 9 - 11  |

| PHYSICAL DIE STRUCTURES        | Figures 12 - 46 |

| COLOR DRAWING OF DIE STRUCTURE | Figure 47       |

| MEMORY CELL                    | Figures 48 - 52 |

| TEM CROSS SECTIONS             | Figures T1 - T7 |

Figure 1. Package photographs of the AMD K6 Microprocessor. Mag. 1.3x.

Figure 2. Topological x-ray view of the package. Mag. 2x.

Figure 4. Package section views illustrating general construction.

Mag. 16x

| Mag. | 80x |

|------|-----|

| mag. | 004 |

Figure 5. Package section views of the lid structure.

Mag. 65x

Mag. 320x

Figure 6. Package section views illustrating external lead connection.

Mag. 500x

Figure 7. Package section views of a typical solder ball connection.

Mag. 100x

# Figure 8. Package section views of a capacitor attach and an internal via.

Figure 9. Whole die photograph of the AMD K6 Microprocessor. Mag. 15x.

Figure 11. Optical views of die corners. Mag 225x.

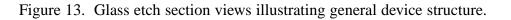

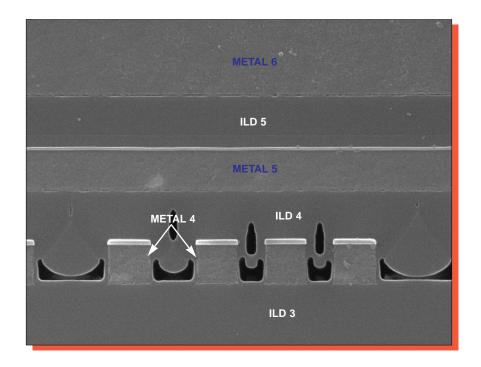

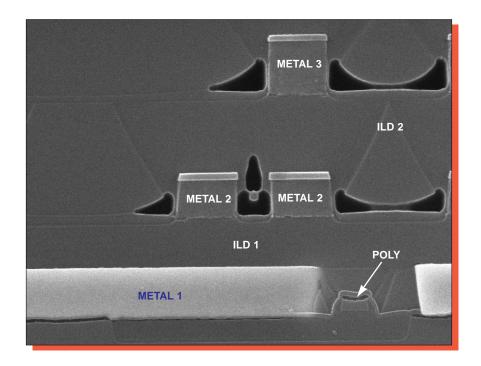

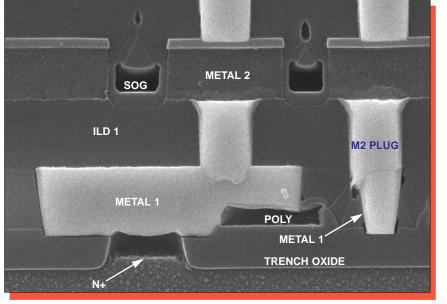

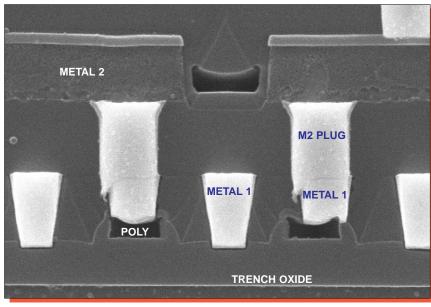

Figure 12. SEM section view illustrating general device structure. Mag. 17,400x.

#### Integrated Circuit Engineering Corporation

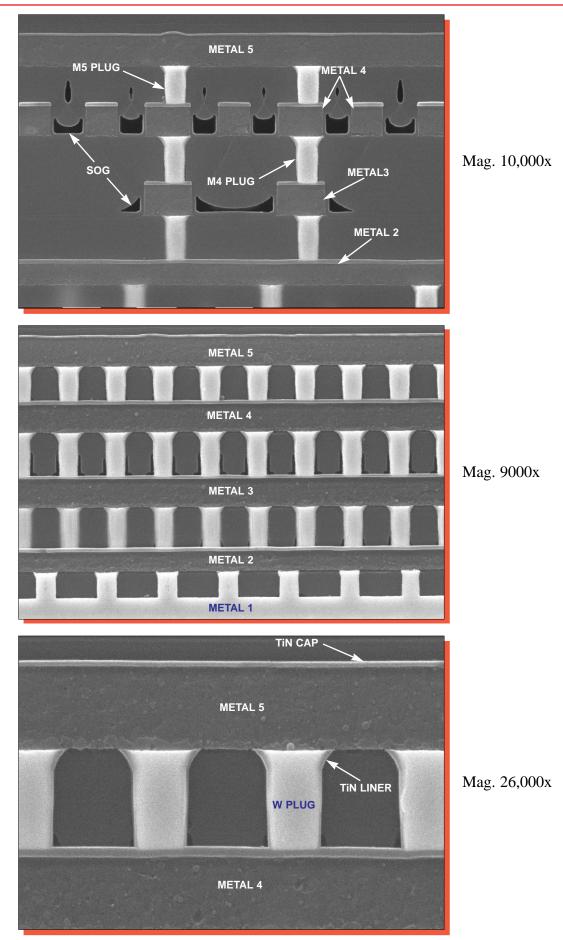

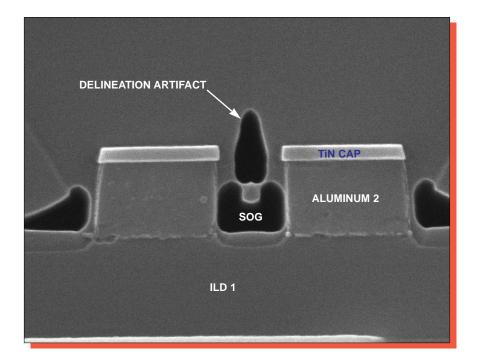

Figure 12a. SEM section views illustrating general device structure.

#### Integrated Circuit Engineering Corporation

Mag. 10,000x.

# Figure 14. SEM section views of metal 6 line profiles.

Mag. 1250x

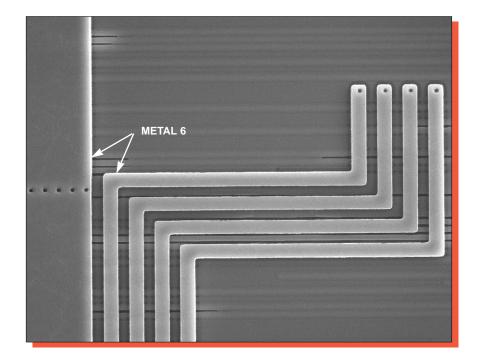

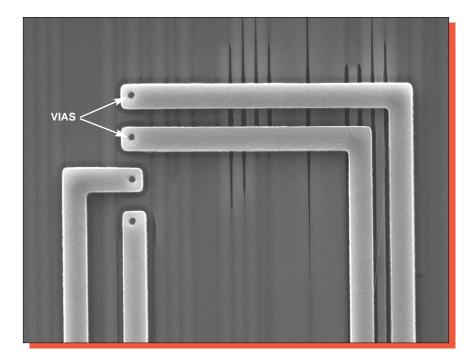

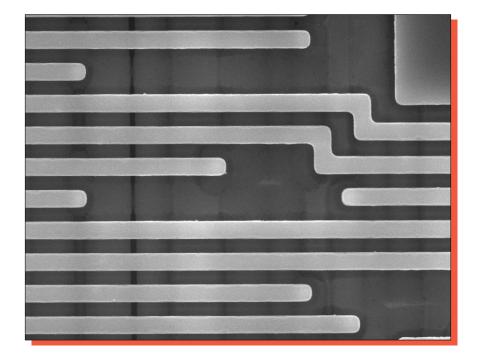

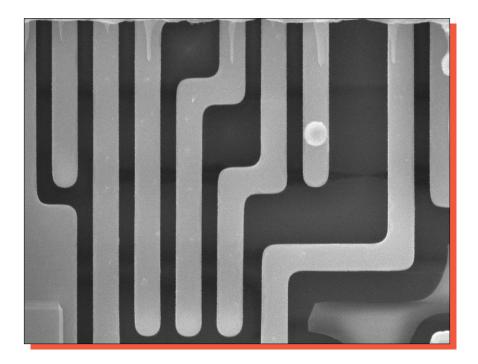

Figure 15. Topological SEM views of metal 6 patterning.  $0^{\circ}$ .

Mag. 2800x

Cu

METAL 5

Mag. 15,000x

Mag. 17,500x

Mag. 12,400x

Figure 18. SEM section views of metal 5 line profiles.

Mag. 9000x

# Figure 20. SEM section views of metal 5 coverage. $60^{\circ}$ .

Mag. 28,000x

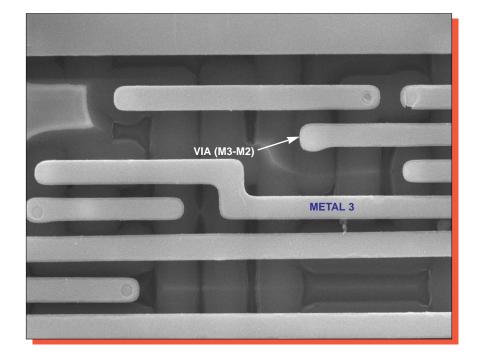

Figure 22. SEM section views of metal 5-to-metal 4 vias.

Mag. 17,000x

Mag. 52,000x

Mag. 13,000x

Figure 23. SEM section views of metal 4 line profiles.

Mag. 10,000x

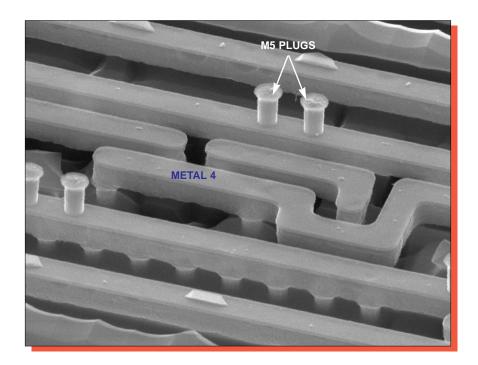

## Figure 25. SEM views of metal 4 coverage. $55^{\circ}$ .

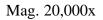

Mag. 20,000x

Mag. 12,000x

Mag. 15,000x

## Figure 28. SEM section views of metal 3 line profiles.

Mag. 7000x

Figure 29. Topological SEM views of metal 3 patterning.  $0^{\circ}$ .

Mag. 13,500x

Figure 30. SEM views of metal 3 coverage.  $60^{\circ}$ .

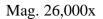

Figure 32. SEM section views of metal 3-to-metal 2 vias.

Mag. 17,600x

Figure 33. SEM section views of metal 2 line profiles.

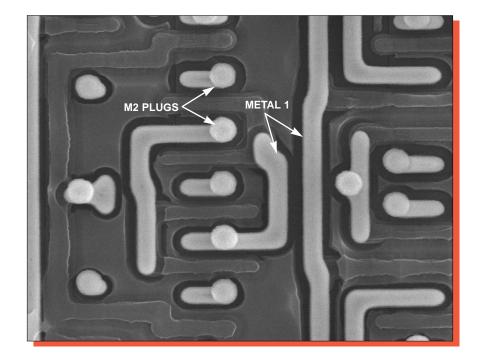

Figure 34. Topological SEM views of metal 2 patterning. 0°.

Mag. 9000x

Mag. 30,000x

Mag. 10,000x

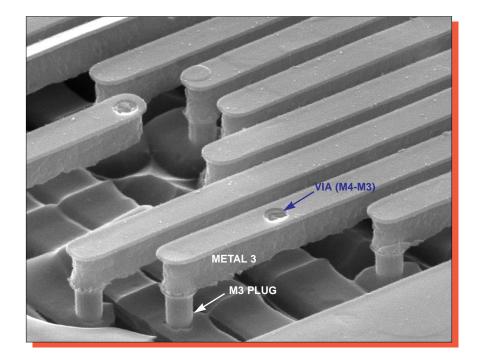

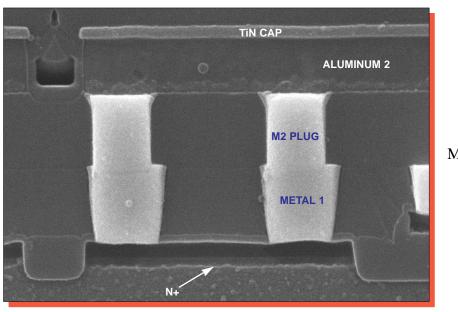

TIN CAP ALUMINUM 2 W PLUG METAL 2 METAL 2 METAL 1

Figure 35. SEM views of metal 2 coverage. 55°.

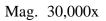

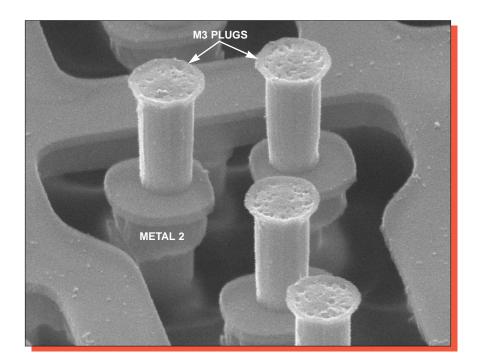

Figure 36. SEM views of metal 2 plugs.  $50^{\circ}$ .

Mag. 25,000x

Mag. 26,000x

Mag. 26,000x

Figure 39. SEM views of general metal 1 coverage. 55°.

Figure 40. SEM section views of metal 1 contacts.

Figure 41. Topological SEM views of poly patterning.  $0^{\circ}$ .

Mag. 9000x

Mag. 15,000x

Mag. 35,000x

Mag. 26,000x

Mag. 52,000x

Figure 43. SEM section views of N-channel transistors.

P-channel

Figure 44. SEM section views of typical transistors. Mag. 52,000x.

glass etch

Figure 45. SEM section views of trench oxide isolation. Mag. 40,000x.

AMD K6 Processor

Orange = Nitride, Blue = Metal, Yellow = Oxide, Green = Poly,

Red = Diffusion, and Gray = Substrate

metal 3

metal 2

delayered

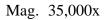

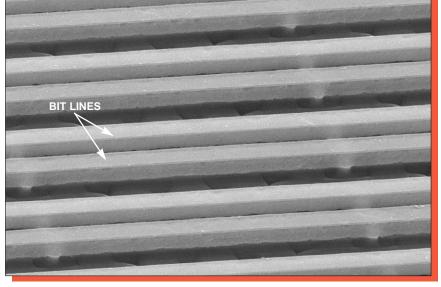

Figure 48. Perspective SEM views of the Cache SRAM array. Mag. 6500x, 55°.

metal 2

metal 1

delayered

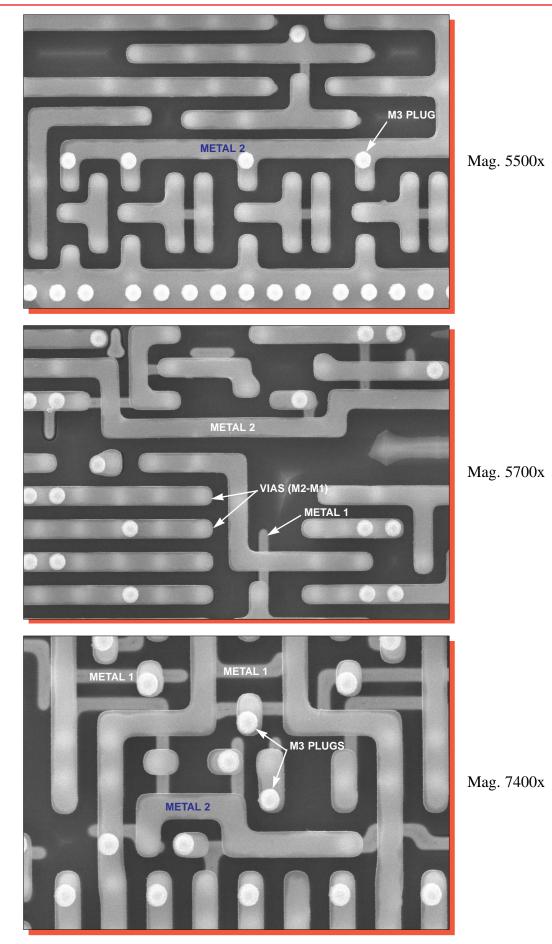

Figure 50. Topological SEM views of the Cache SRAM array. Mag. 6200x,  $0^{\circ}$ .

metal 1

delayered

metal 1

delayered

Figure T1. TEM overview of general structure. Mag. 12,400x.

Mag. 29,750x

Figure T2. TEM section view of metal 6 with detail of cap and barrier.

Mag. 57,600x

Mag. 31,500x

Figure T3. TEM section views of delamination at aluminum and contact structures.

Mag. 76,500x

Mag. 180,000x

Figure T4. TEM section views of contact voids.

Mag. 76,500x

Mag. 243,000x

Figure T6. TEM section views of gate parallel to gate length.

Mag. 186,000x

Mag. 196,000x

Figure T7. TEM section details of diffusion contact and gate.