# **Construction Analysis**

# Atmel AT27C512R 512K UVEPROM

# **INDEX TO TEXT**

| TITLE                      | PAGE  |

|----------------------------|-------|

| INTRODUCTION               | 1     |

| MAJOR FINDINGS             | 1     |

| TECHNOLOGY DESCRIPTION     |       |

| Assembly                   | 2     |

| Die Process                | 2 - 3 |

| ANALYSIS RESULTS I         |       |

| Assembly                   | 4     |

| ANALYSIS RESULTS II        |       |

| Die Process                | 5 - 6 |

| TABLES                     |       |

| Procedure                  | 7     |

| Overall Quality Evaluation | 8     |

| Package Markings           | 9     |

| Wirebond Strength          | 9     |

| Die Material Analysis      | 9     |

| Horizontal Dimensions      | 10    |

| Vertical Dimensions        | 10    |

## **INTRODUCTION**

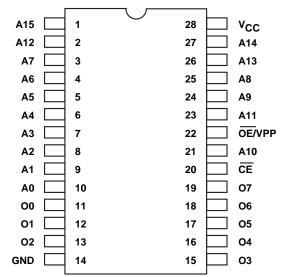

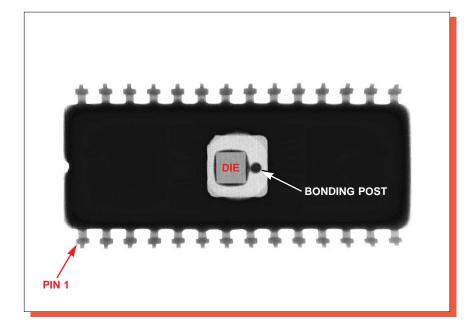

This report describes a construction analysis of the Atmel AT27C512R 512K UVEPROM. Three devices packaged in 28-pin Ceramic Dual In-Line Packages (CERDIPs) with a quartz window were received for the analysis. Devices were date coded 9619.

## **MAJOR FINDINGS**

## **Questionable Items:**<sup>1</sup>

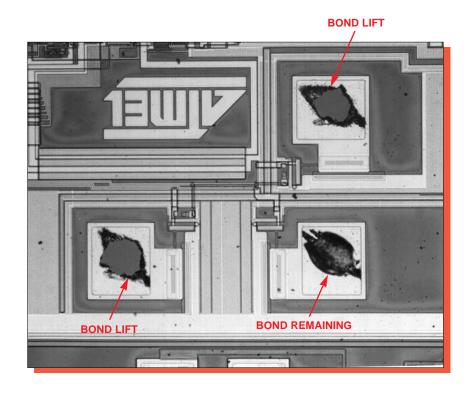

• Several bond lifts occurred during wirepull tests on Samples 2 and 3.

## **Special Features:**

- Titanium silicided diffusions.

- Tungsten plugs used at all contacts.

- Planarized final passivation.

<sup>1</sup>*These items present possible quality or reliability concerns. They should be discussed with the manufacturer to determine their possible impact on the intended application.*

## **TECHNOLOGY DESCRIPTION**

## Assembly:

- Devices were packaged in 28-pin Ceramic Dual In-Line Packages (CERDIPs). A quartz window was present over the die.

- The package consisted of two ceramic halves held together by a glass frit. The die was mounted to the cavity floor using a silver-filled glass.

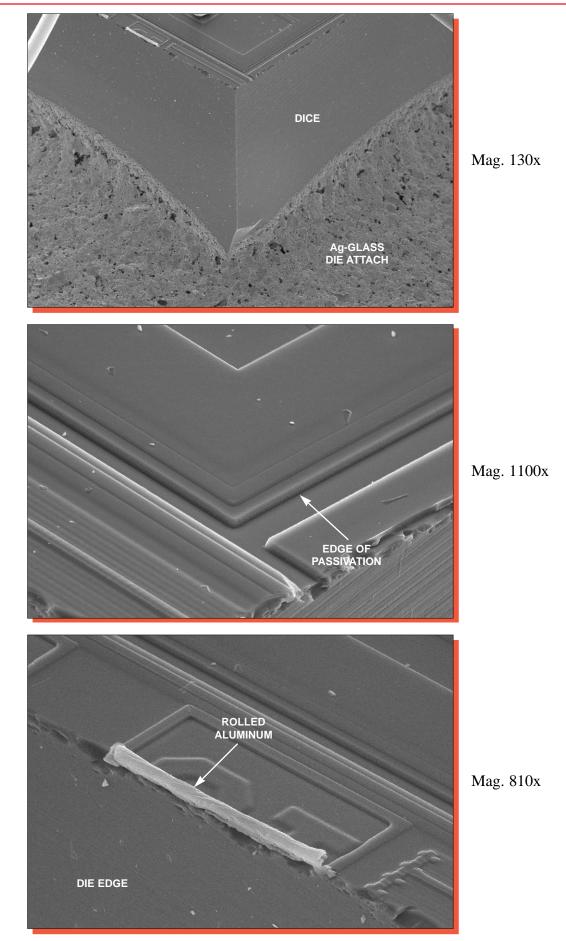

- Die separation was by sawing.

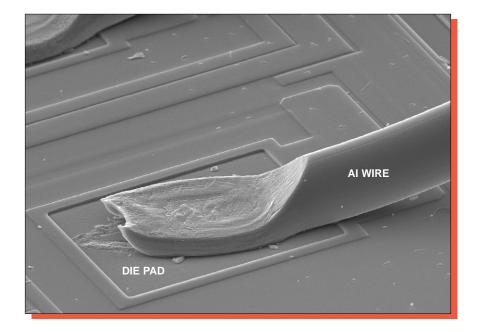

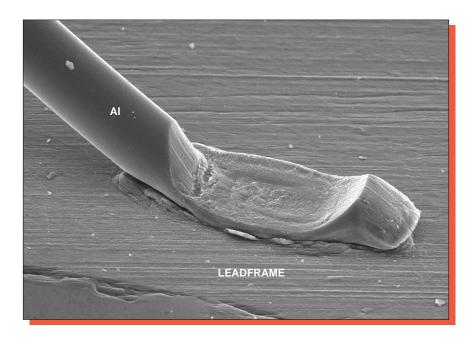

- Wirebonding was by the ultrasonic wedge bond method (backward bonded) using 1.3 mil O.D. aluminum wire.

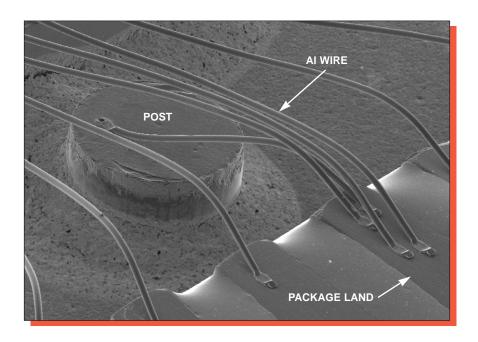

- All pins were connected and pins 14 and 28 (Vcc and GND) had multiple bonding wires. A cavity bonding post was employed which biased the substrate to GND.

## **Die Process:**

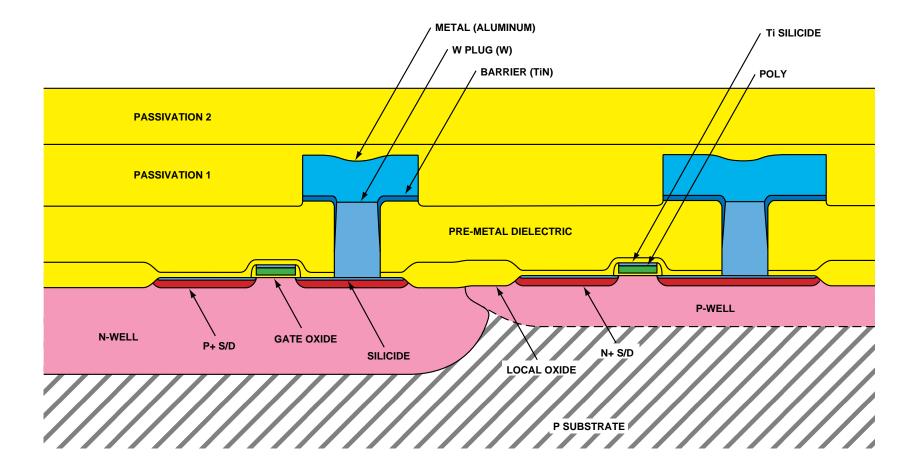

- Devices were fabricated using a selective oxidation, twin-well CMOS process in a P substrate. No epi was used.

- No die coat was present.

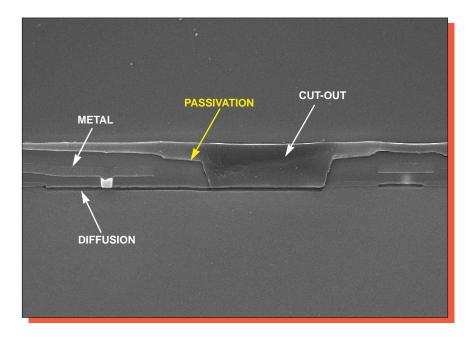

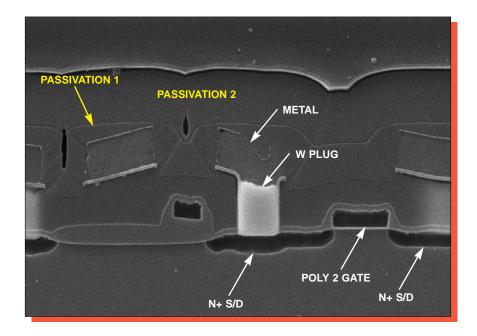

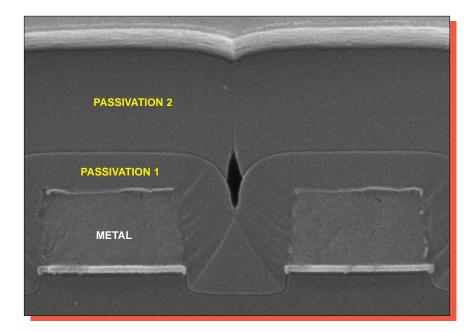

- Passivation consisted of a layer of oxynitride over a layer of silicon-dioxide. The SiO<sub>2</sub> had been given a minimal planarizing etch.

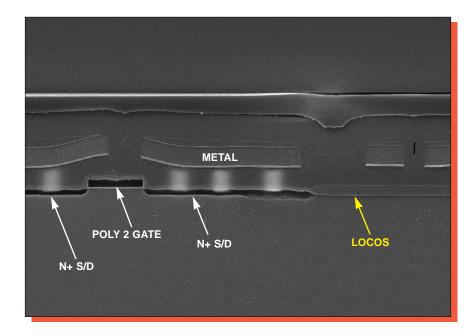

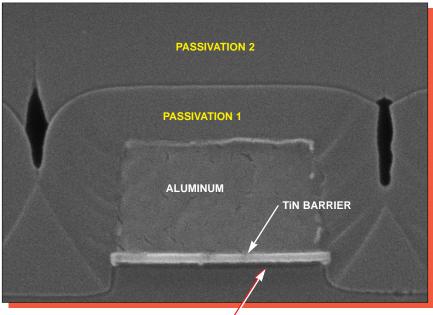

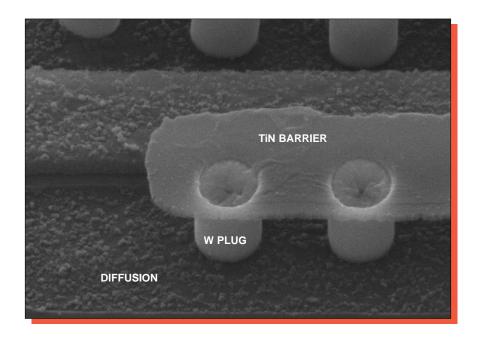

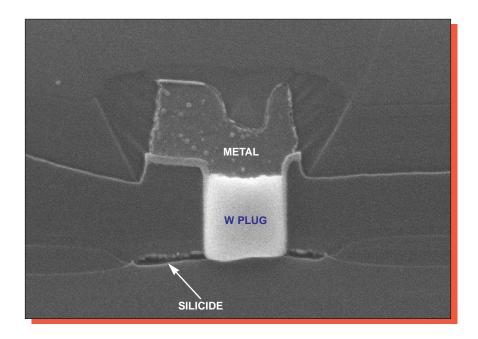

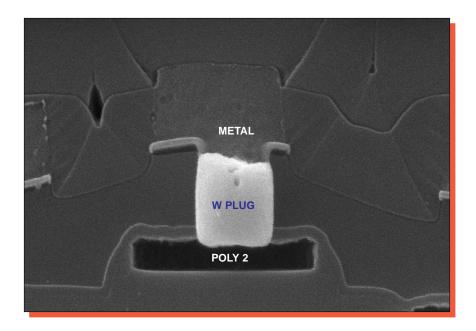

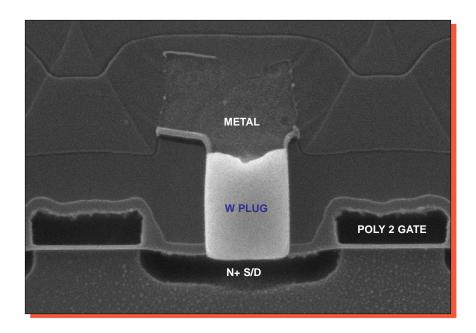

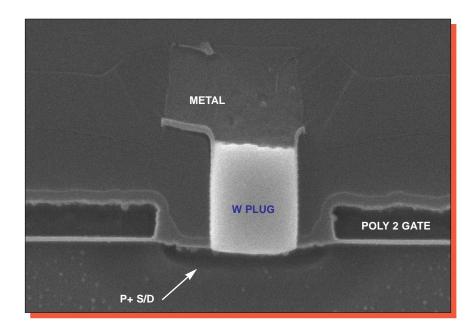

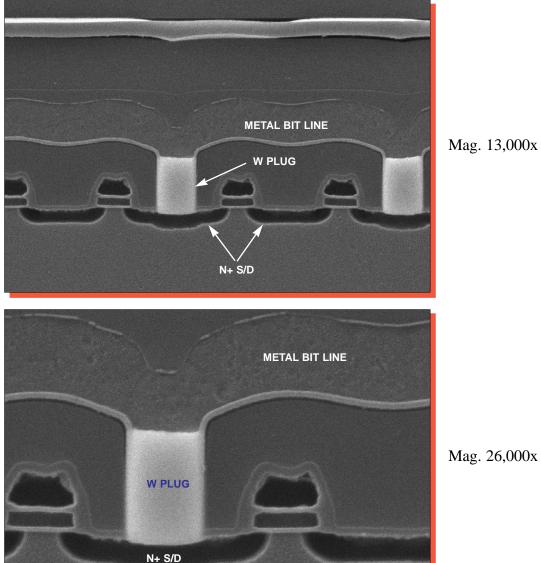

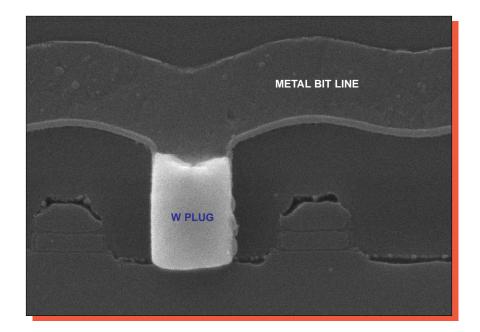

- Metallization consisted of a single layer of aluminum with a titanium-nitride barrier and a titanium adhesion layer. Tungsten plugs were used at all contacts.

- Pre-metal dielectric consisted of a layer of borophosphosilicate glass (BPSG) over densified oxides. The glass was reflowed prior to contact cuts only.

## **<u>TECHNOLOGY DESCRIPTION</u>** (continued)

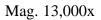

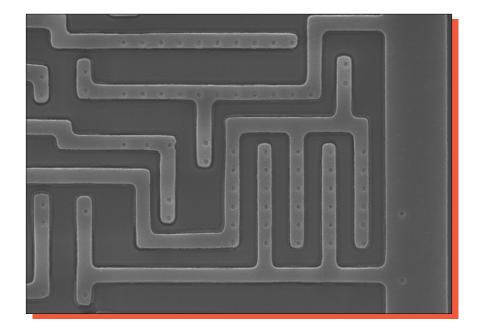

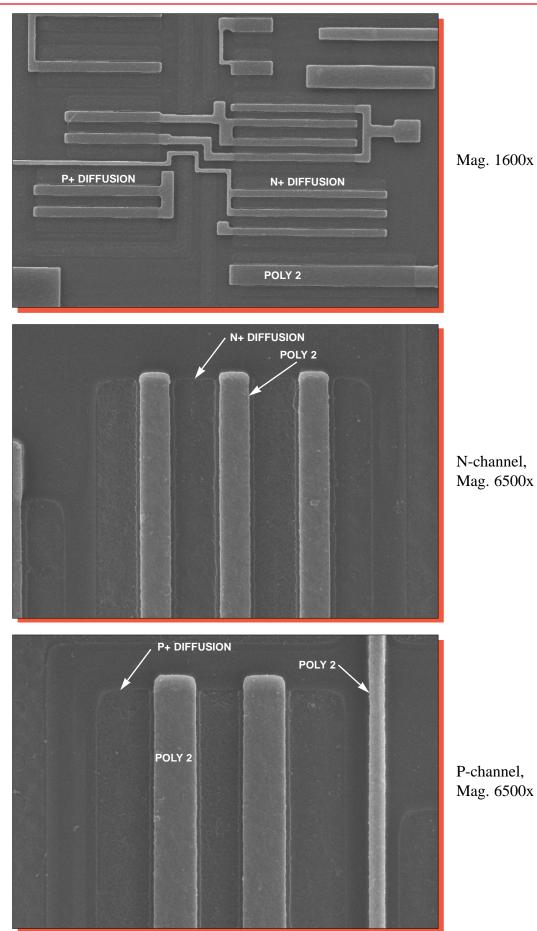

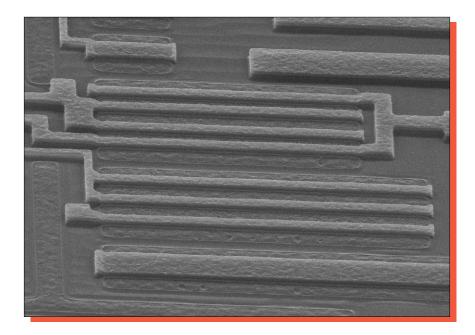

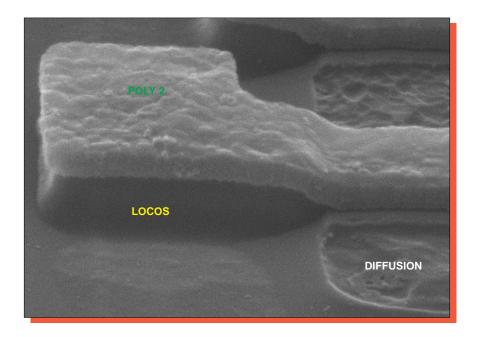

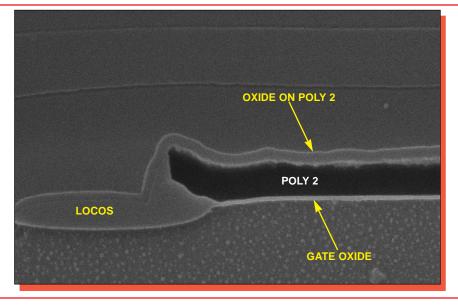

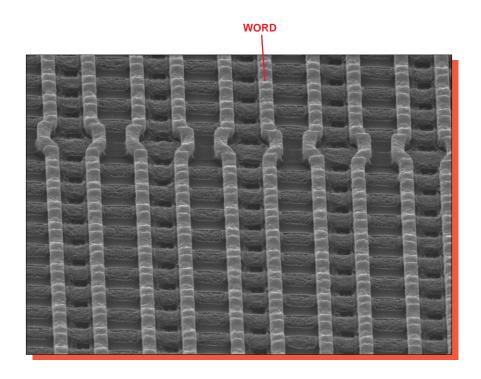

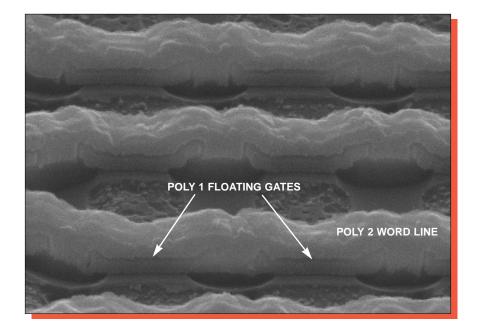

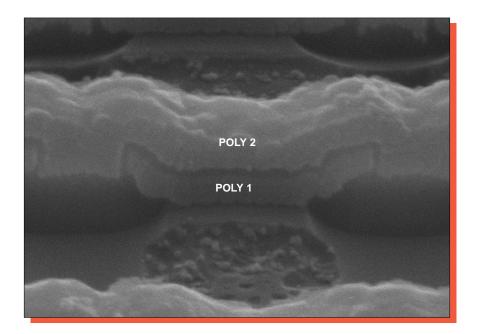

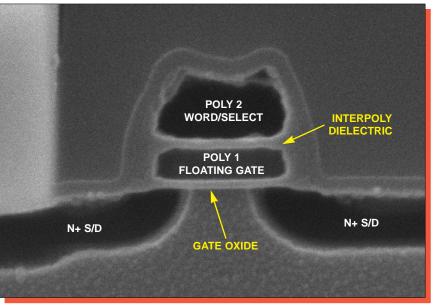

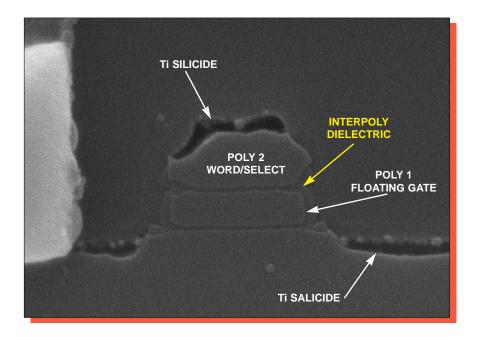

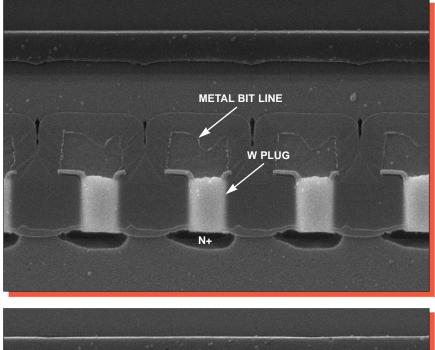

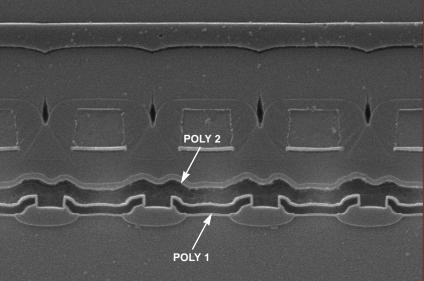

- Two layers of poly were used on the die. Polycide 2 (poly and titanium silicide) was used to form all gates on the die and the select/word lines in the EPROM cell array. Poly 1 (no silicide) was used exclusively in the cell to form the floating gates. Direct poly-to-diffusion (buried) contacts were not used. Interpoly dielectric consisted of oxide only. Definition of the poly was by a dry etch of normal quality.

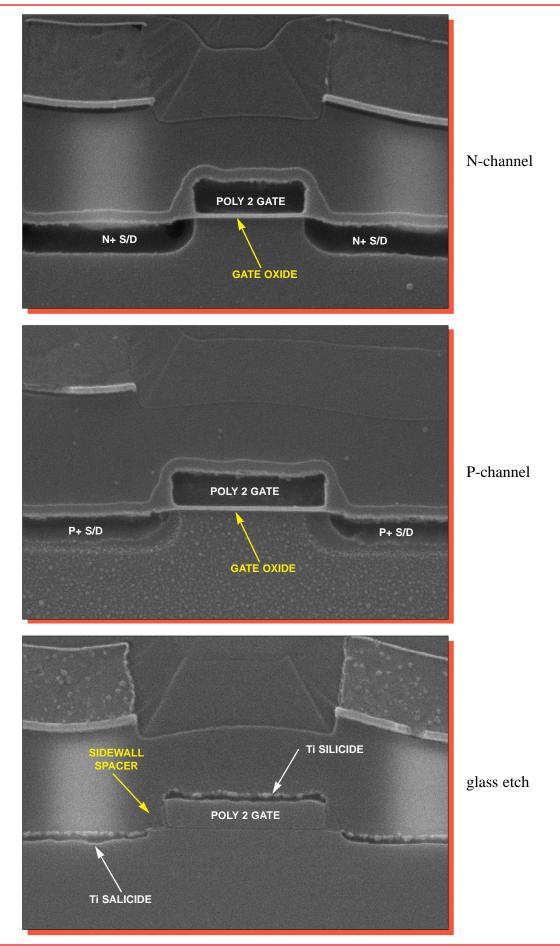

- Standard implanted N+ and P+ diffusions formed the sources/drains of the CMOS transistors. An LDD process was used with oxide sidewall spacers left in place. A titanium silicide was present on all diffusions (salicide process).

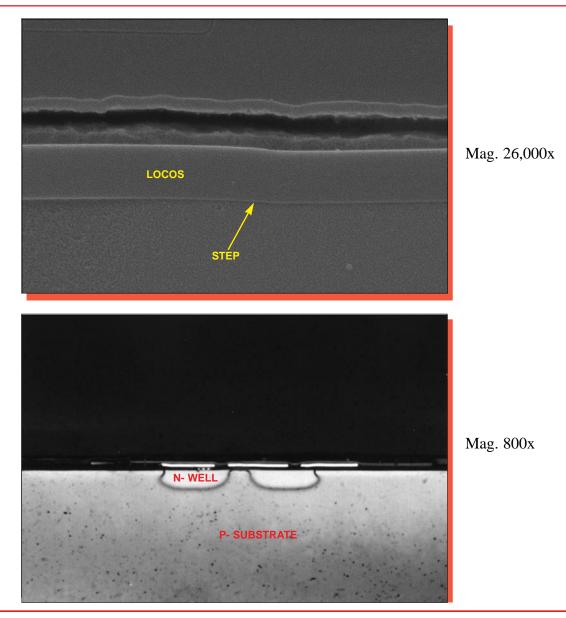

- Local oxide (LOCOS) isolation. A slight step was present in the oxide at the edge of the well indicating a twin-well process was used.

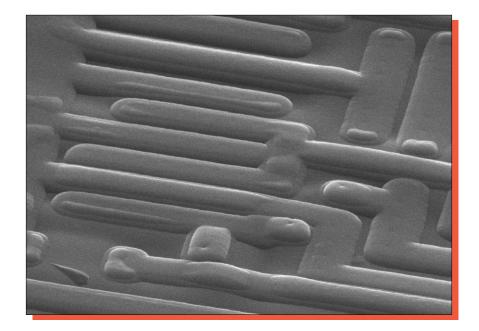

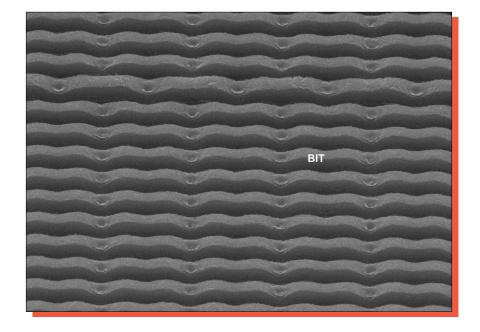

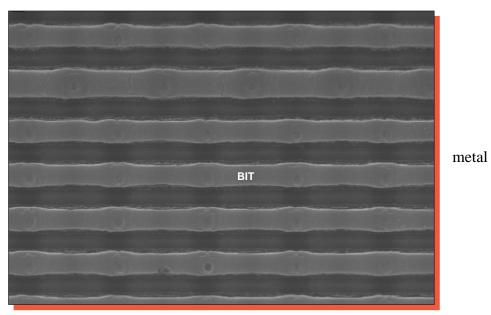

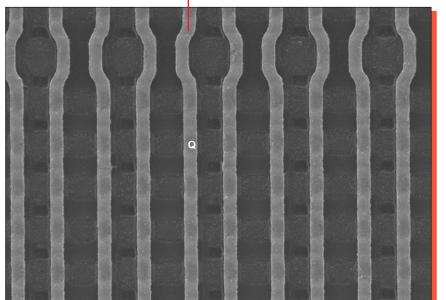

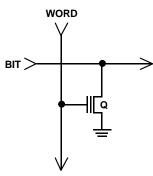

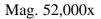

- The memory cells used a stacked poly EPROM design. Metal was used to form the bit lines. Polycide 2 was used to form the word/select lines, and poly 1 was used exclusively to form the floating gates.

- Redundancy fuses were not present.

## ANALYSIS RESULTS I

## Package and Assembly:

**Figures 1 - 7**

## **Questionable Items:**<sup>1</sup>

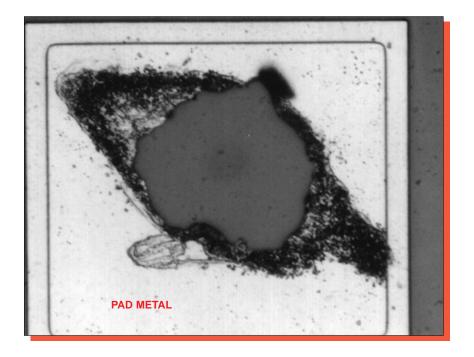

• Wirepull tests caused several bond lifts (Figure 7).

### **General Items:**

- Devices were packaged in 28-pin Ceramic Dual In-Line Packages (CERDIPs) with quartz windows.

- Overall package quality: Good. No significant defects were noted in the external or internal portions of the package. No cracks or chips were noted in the ceramic or glass frit seal.

- Leadframe: The leadframe was constructed of iron-nickel. No voids or cracks were noted at lead exits.

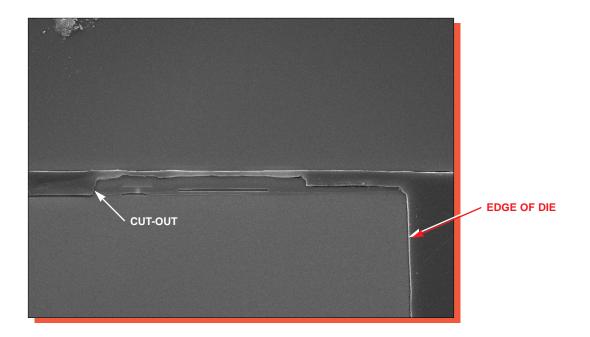

- Die dicing: Die separation was by sawing of normal quality. No large cracks or chips were present. A silver-filled glass was used to attach the die to the header. Rolled aluminum due to the sawing was present in the scribe lane. This could shake loose in some cases and possibly cause a short to occur.

- Wirebonding was by the ultrasonic wedge bond method using 1.3 mil O.D. aluminum wire. The clearance of the wires from the edge of the die was minimal due to the backward bonding technique used. Most bond pull strengths were normal; however, seven bond lifts occurred on Sample 2 out of the 24 wires tested, and two bond lifts occurred on Sample 3 out of 24 wires tested. The bonds lifted at an average force of 3.5 grams. A cavity bonding post was employed which biased the substrate to GND.

<sup>1</sup>*These items present possible quality or reliability concerns. They should be discussed with the manufacturer to determine their possible impact on the intended application.*

## ANALYSIS RESULTS II

### **Die Process:**

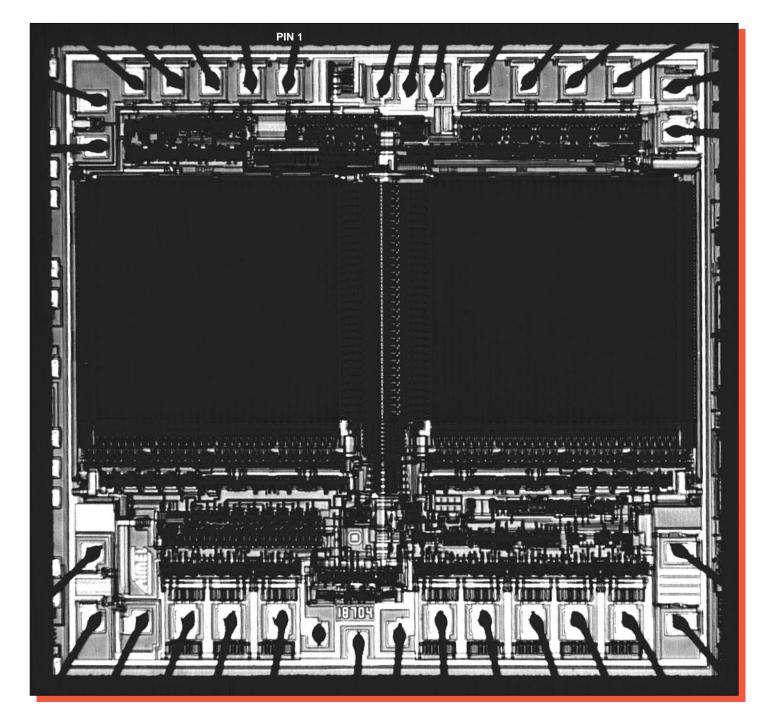

**Figures 8 - 28**

### **Questionable Items:**<sup>1</sup> None.

#### **Special Features:**

- Tungsten plugs used at all contacts.

- Titanium-silicided diffusions.

#### **General Items:**

- Fabrication process: Devices were fabricated using a selective oxidation, twin-well CMOS process in a P substrate. No epi was used.

- Process implementation: Die layout was clean and efficient. Alignment was good at all levels. No damage or contamination was found.

- Die coat: No die coat was present.

- Overlay passivation: A layer of oxynitride over a layer of silicon-dioxide. As mentioned, the first layer (SiO<sub>2</sub>) had been given a slight planarizing etch. Overlay integrity test indicated defect-free passivation. Edge seal was good.

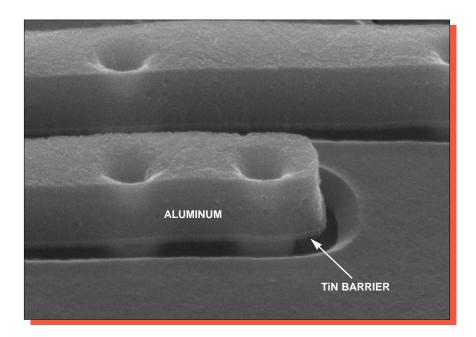

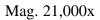

- Metallization: A single layer of metal consisting of aluminum with a titanium-nitride barrier and a titanium adhesion layer. Tungsten plugs were used at all contacts.

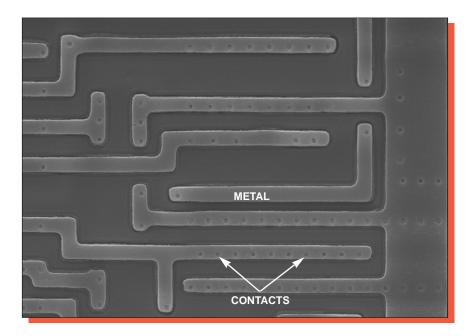

- Metal patterning: The metal layer was patterned by a dry etch of normal quality. Alol contacts were completely surrounded by aluminum.

<sup>1</sup>*These items present possible quality or reliability concerns. They should be discussed with the manufacturer to determine their possible impact on the intended application.*

## ANALYSIS RESULTS II (continued)

- Metal defects: No voiding, notching, or neckdown was noted in the metal layer. No silicon nodules were noted following the removal of the metal layer.

- Metal step coverage: Aluminum thinning did not exceed 40 percent due to the presence of the tungsten plugs. MIL-STD allows up to 70 percent metal thinning for contacts of this size.

- Pre-metal dielectric: A layer of borophosphosilicate glass (BPSG) over various densified oxides was used under the metal. Reflow was performed prior to contact cuts only. No problems were found.

- Contact defects: Contact cuts were defined by dry-etch process. Minor over-etching of the contacts was noted, but is not considered to be a problem.

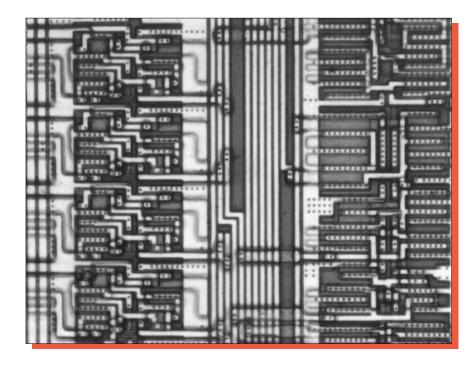

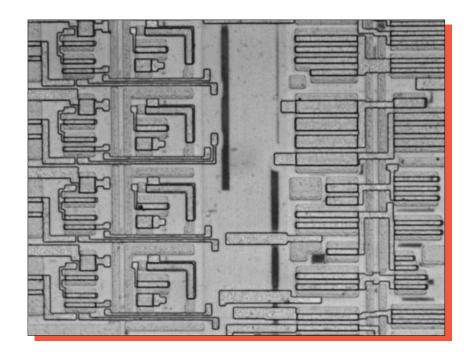

- Polysilicon: Two layers of poly were used on the die. Polycide 2 (poly and titanium silicide) was used to form all gates on the die and the select/word lines in the EPROM cell array. Poly 1 (no silicide) was used exclusively in the cell to form the floating gates. Direct poly-to-diffusion (buried) contacts were not used. Interpoly dielectric consisted of oxide only. Definition was by a dry etch of normal quality.

- Implanted N+ and P+ diffusions formed the sources/drains of the CMOS transistors. An LDD process was used with oxide sidewall spacers left in place. Titanium silicide was present over all diffusions (salicide process).

- Local oxide (LOCOS) isolation was used. No problems were noted. The slight step present in the oxide at the well boundary indicates a twin-well process was employed.

- EPROM: Memory cell consisted of a stacked poly EPROM design. Metal was used to form the bit lines. Poly 2 was used to form the word/select lines, and poly 1 was used exclusively to form the floating gates. Interpoly dielectric consisted of oxide only. Cell pitch was 2.2 x 2.3 microns.

- Redundancy fuses were not present on the die.

#### **PROCEDURE**

The devices were subjected to the following analysis procedures:

External inspection X-ray Delid Internal optical inspection SEM of passivation and assembly features Passivation integrity test Passivation integrity test Wirepull test Passivation removal SEM inspection of metal Metal removal and inspect barrier Delayer to silicon and inspect poly/die surface Die sectioning (90° for SEM)\* Die material analysis Measure horizontal dimensions

\*Delineation of cross-sections is by silicon etch unless otherwise indicated.

## **OVERALL QUALITY EVALUATION:** Overall Rating: Good

## **DETAIL OF EVALUATION**

| Package integrity                        | Ν                                                   |

|------------------------------------------|-----------------------------------------------------|

| Package markings                         | Ν                                                   |

| Die placement                            | Ν                                                   |

| Wirebond placement                       | Ν                                                   |

| Wire spacing                             | Ν                                                   |

| Wirebond quality                         | NP*                                                 |

| Die attach quality                       | Ν                                                   |

| Dicing quality                           | Ν                                                   |

| Die attach method                        | Silver-filled glass                                 |

| Dicing method                            | Sawn                                                |

| Wirebond method                          | Ultrasonic wedge bonds using 1.3 mil aluminum wire. |

| Die surface integrity:                   |                                                     |

| Toolmarks (absence)                      | G                                                   |

| Particles (absence)                      | G                                                   |

| Contamination (absence)                  | G                                                   |

| Process defects (absence)                | G                                                   |

| General workmanship                      | G                                                   |

| Passivation integrity                    | G                                                   |

| Metal definition                         | Ν                                                   |

| Metal integrity                          | Ν                                                   |

| ~                                        |                                                     |

| Contact coverage                         | G                                                   |

| Contact coverage<br>Contact registration | G<br>G                                              |

\*Bond lifts on Samples 2 and 3.

*G* = *Good*, *P* = *Poor*, *N* = *Normal*, *NP* = *Normal/Poor*

## PACKAGE MARKINGS (TOP)

### ATMEL LOGO AT27C512R 20DMA 9619

## (BOTTOM)

#### 5DO314-18704C 1 PHILIPPINES - F 5D9601

### **WIREBOND STRENGTH**

| Wire material:        | 1.3 mil O.D. aluminum | 1    |

|-----------------------|-----------------------|------|

| Die pad material:     | aluminum              |      |

| <u>Sample #</u>       | 2                     | 3    |

| # of wires pulled:    | 24                    | 24   |

| Bond lifts:           | 7                     | 2    |

| Force to break - high | n: 6g                 | 6g   |

| - low                 | : 3g                  | 2.5g |

| - avg                 | .: 4.3g               | 4.1g |

| - std.                | dev.: 0.8             | 1.1  |

## **DIE MATERIAL ANALYSIS**

| Overlay passivation:  | A layer of oxynitride over a layer of silicon dioxide.                                                                         |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Metallization:        | Aluminum (Al) with a titanium-nitride (TiN) barrier and a titanium adhesion layer.                                             |

| Polycide 2:           | Titanium (Ti) silicide.                                                                                                        |

| Salicide:             | Titanium (Ti) silicide.                                                                                                        |

| Pre-metal dielectric: | A layer of borophosphosilicate glass (BPSG) containing 3.5 wt. % phosphorus and 3.0 wt. % boron over various densified oxides. |

### **HORIZONTAL DIMENSIONS**

| Die size:                                                                                                          | 3.4 x 3.2 mm (133 x 125 mils)                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Die area:                                                                                                          | 10.9 mm <sup>2</sup> (16,625 mils <sup>2</sup> )                                                                                                        |

| Min pad size:                                                                                                      | 0.11 x 0.13 mm (4.5 x 5.0 mils)                                                                                                                         |

| Min pad window:                                                                                                    | 0.1 x 0.11 mm (3.8 x 4.5 mils)                                                                                                                          |

| Min pad space:                                                                                                     | 18 microns                                                                                                                                              |

| Min metal width:                                                                                                   | 1.3 micron                                                                                                                                              |

| Min metal space:                                                                                                   | 1.1 micron                                                                                                                                              |

| Min metal pitch:                                                                                                   | 2.4 microns                                                                                                                                             |

| Min contact:                                                                                                       | 0.8 micron                                                                                                                                              |

| Min poly 2 width:                                                                                                  | 0.55 micron                                                                                                                                             |

| Min poly 2 space:                                                                                                  | 0.6 micron                                                                                                                                              |

| Min gate length - (N-channel):*<br>- (P-channel):*<br>N-channel gate length in array:<br>Cell size:<br>Cell pitch: | <ul> <li>1.1 micron (peripheral circuits)</li> <li>1.55 micron</li> <li>0.7 micron</li> <li>5 microns<sup>2</sup></li> <li>2.2 x 2.3 microns</li> </ul> |

\**Physical gate length.*

## **VERTICAL DIMENSIONS**

Die thickness:

0.5 mm (19 mils)

#### Layers:

Passivation 2: Passivation 1: Metal - aluminum: - barrier: Pre-metal dielectric: Oxide on poly 2: Poly 2 - silicide: - poly: Interpoly dielectric: Poly 1: Local oxide: N+ S/D: P + S/D: N-well: P-well: 1.0 micron 0.35 micron 0.8 micron 0.05 micron (approximate) 0.4 - 0.95 micron 0.1 micron 0.05 micron (approximate) 0.25 micron 0.05 micron 0.35 micron 0.35 micron 0.25 micron 0.35 micron 0.3 micron 0.3 micron 0.3 micron 0.3 micron 0.3 micron 0.3 micron 0.1 micron 0.25 micron 0.3 micron 0.3 micron

## **HORIZONTAL DIMENSIONS**

| Die size:                       | 3.4 x 3.2 mm (133 x 125 mils)                    |

|---------------------------------|--------------------------------------------------|

| Die area:                       | 10.9 mm <sup>2</sup> (16,625 mils <sup>2</sup> ) |

| Min pad size:                   | 0.11 x 0.13 mm (4.5 x 5.0 mils)                  |

| Min pad window:                 | 0.1 x 0.11 mm (3.8 x 4.5 mils)                   |

| Min pad space:                  | 18 microns                                       |

| Min metal width:                | 1.3 micron                                       |

| Min metal space:                | 1.1 micron                                       |

| Min metal pitch:                | 2.4 microns                                      |

| Min contact:                    | 0.8 micron                                       |

| Min poly 2 width:               | 0.55 micron                                      |

| Min poly 2 space:               | 0.6 micron                                       |

| Min gate length - (N-channel):* | 1.1 micron (peripheral circuits)                 |

| - (P-channel):*                 | 1.55 micron                                      |

| N-channel gate length in array: | 0.7 micron                                       |

| Cell size:                      | 5 microns <sup>2</sup>                           |

| Cell pitch:                     | 2.2 x 2.3 microns                                |

|                                 |                                                  |

\*Physical gate length.

## VERTICAL DIMENSIONS

Die thickness:

0.5 mm (19 mils)

## Layers:

| Passivation 2:        | 1.0 micron                |

|-----------------------|---------------------------|

| Passivation 1:        | 0.35 micron               |

| Metal - aluminum:     | 0.8 micron                |

| - barrier:            | 0.05 micron (approximate) |

| Pre-metal dielectric: | 0.4 - 0.95 micron         |

| Oxide on poly 2:      | 0.1 micron                |

| Poly 2 - silicide:    | 0.05 micron (approximate) |

| - poly:               | 0.25 micron               |

| Interpoly dielectric: | 0.05 micron (approximate) |

| Poly 1:               | 0.15 micron               |

| Local oxide:          | 0.35 micron               |

| N+ S/D:               | 0.25 micron               |

| P + S/D:              | 0.3 micron                |

| N-well:               | 4.5 microns (approximate) |

| P-well:               | Could not delineate       |

## **INDEX TO FIGURES**

| ASSEMBLY                       | Figures 1 - 7   |

|--------------------------------|-----------------|

| DIE LAYOUT AND IDENTIFICATION  | Figures 8 - 9   |

| PHYSICAL DIE STRUCTURES        | Figures 10 - 28 |

| COLOR DRAWING OF DIE STRUCTURE | Figure 21a      |

| EPROM MEMORY CELLS             | Figures 22 - 26 |

| INPUT PROTECTION               | Figure 27       |

| GENERAL CIRCUIT LAYOUT         | Figure 28       |

- ii -

Figure 3. Perspective SEM views of dicing, die attach, and edge seal. 60°.

## Mag. 1600x

Mag. 30x

Figure 5. SEM views illustrating backward wirebonding. 60°.

Mag. 160x

Mag. 800x

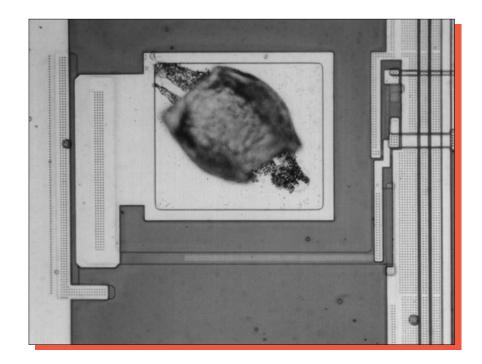

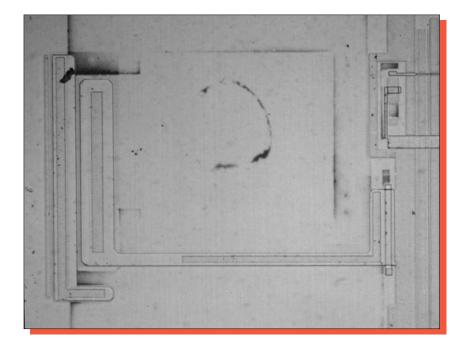

Figure 7. Optical views of bond lifts following wire pull test.

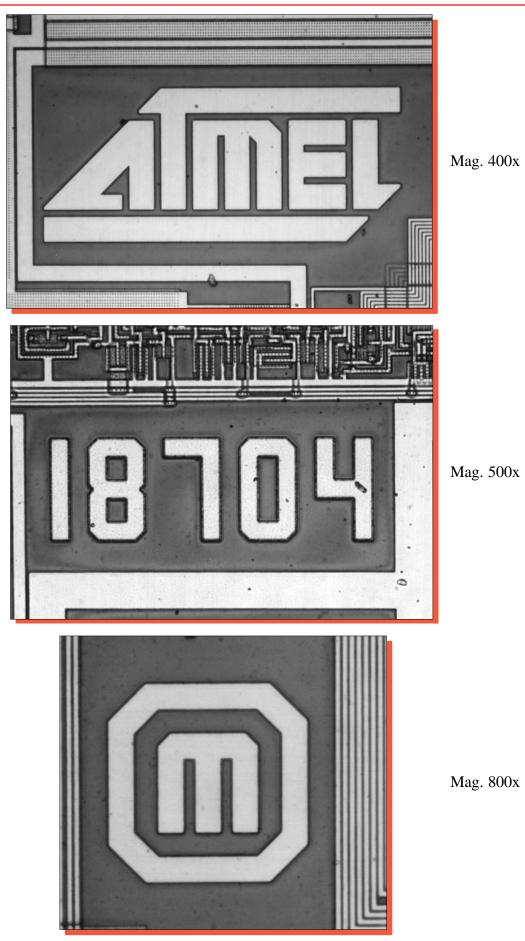

Figure 9. Optical views of markings on the die surface.

## Mag. 6500x

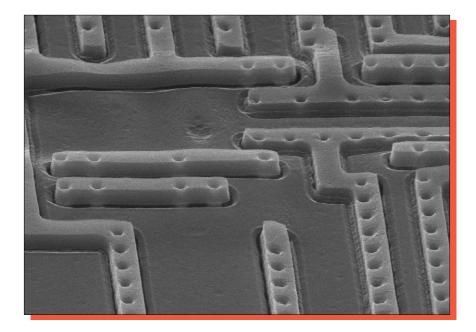

Figure 10. SEM section views of general construction.

Mag. 4000x

Mag. 26,000x

Ti ADHESION LAYER

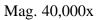

Mag. 40,000x

Figure 12. SEM section views of metal line profiles.

Mag. 5200x

Figure 14. SEM views illustrating metal step coverage.  $60^{\circ}$ .

## metal-to-poly

metal-to-diffusion

metal-to-diffusion, glass etch, Mag. 26,000x

metal-to-poly 2, silicon etch, Mag. 26,000x

### metal-to-N+

## Figure 17. SEM section views of typical metal contacts. Mag. 26,000x.

Figure 18. Topological SEM views of poly 2 patterning.  $0^{\circ}$ .

Mag. 3600x

Figure 20. SEM section views of typical transistors. Mag. 26,000x.

Figure 20a. SEM section view of a local oxide birdsbeak. Mag. 26,000x.

Figure 21. SEM section views of the well structure.

Orange = Nitride, Blue = Metal, Yellow = Oxide, Green = Poly,

Red = Diffusion, and Gray = Substrate

Figure 21a. Color cross section drawing illustrating device structure.

metal

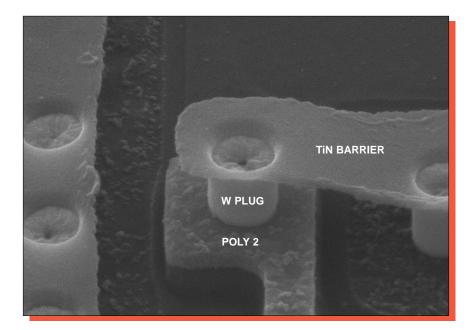

unlayered

Mag. 21,000x

WORD

unlayered

## Mag. 52,000x

Mag. 26,000x

Mag. 13,000x

Mag. 13,000x

Mag. 52,000x

intact

## unlayered

Figure 27. Optical views of input protection. Mag. 400x.

intact

unlayered

Figure 28. Optical views of general circuitry. Mag. 800x.