# High-Performance Internal Product Portfolio Overview

Issue 10 Fourth Quarter, 1995

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and expenses, and controla, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### **PREFACE**

Welcome to the High-Performance Embedded Systems Marketing Group in Austin.

This document has been prepared as a quarterly guide to the broad range of 16- and 32-bit microprocessors available from Motorola. It is intended to be a handy reference guide to Motorola's microprocessor portfolio that complements the other sources of technical product information.

Our High Performance product family is still growing rapidly. The 68000 Family continues to win new customers with increasing levels of integration, low-power operation, and high-performance networking solutions that improve price/performance thus enabling our customers to develop new market segments. The large base of installed software and development environments available for the family make the 68000 Family the processor of choice for the embedded control world.

Because of the increasing complexity and range of our products, the tools we provide to the field need to be appropriate and user friendly. Thus, we have tried to produce this document in a similar format to other offerings from High-Performance Embedded Systems Division.

If you have any questions, please do not hesitate to call either your local High-Performance PME or the factory Technical Marketing Group.

# **Table of Contents**

| Title                                                               | Page |

|---------------------------------------------------------------------|------|

| M68000 Family Strategy                                              | 1    |

| MC68000                                                             |      |

| MC68EC000                                                           |      |

| MC68HC000                                                           |      |

| MC68HC001                                                           | _    |

| MC68008                                                             |      |

| MC68010                                                             |      |

| MC68020                                                             |      |

| MC68EC020                                                           |      |

| MC68030                                                             |      |

| MC68EC030                                                           |      |

| MC68040                                                             |      |

| XC68040V                                                            |      |

| MC68EC/LC040                                                        |      |

| XC68060                                                             |      |

| XC68EC060                                                           |      |

|                                                                     |      |

| XC68LC060                                                           |      |

| XC68852                                                             |      |

| PC68853                                                             |      |

| XCF5102                                                             |      |

| M68300 Family Strategy                                              |      |

| MC68302                                                             |      |

| XC68LC302                                                           |      |

| XC68PM302                                                           |      |

| MC68306                                                             |      |

| XC68307/XC68307V                                                    |      |

| XC68322                                                             |      |

| PC68328V                                                            |      |

| MC68330/MC68330V                                                    |      |

| MC68331                                                             |      |

| MC68332                                                             |      |

| XC68F333                                                            |      |

| MC68340/MC68340V                                                    |      |

| XC68341/XC68341V                                                    |      |

| MC68349/MC68349V "DRAGON I™"                                        | 72   |

| XC68356                                                             |      |

| MC68360 "QUICC"                                                     | 76   |

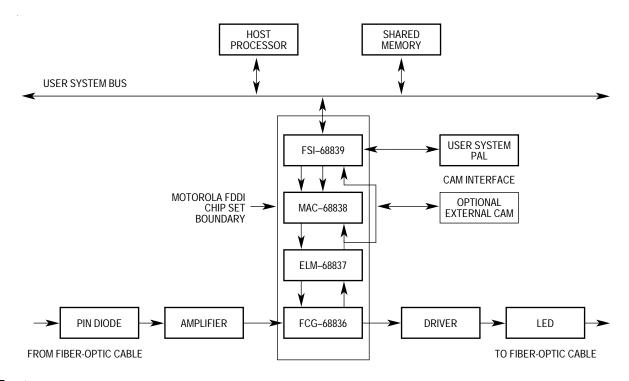

| First-Generation FDDI Chip Set (MC68836, MC68837, MC68838, MC68839) | 80   |

| Next-Generation FDDI Chip Set (XC68834, XC68836, XC68840)           |      |

| FDDI Quad ELM (MC68847)                                             |      |

| Embedded PowerPC Microprocessors                                    |      |

| XPC602                                                              |      |

| XPC603/603e                                                         |      |

| XPC604                                                              |      |

| PPC860                                                              |      |

| Competition.                                                        |      |

| AMD                                                                 |      |

| Hitachi                                                             |      |

| IDT                                                                 |      |

| Intel                                                               |      |

| HILGI                                                               | 90   |

-- - -

| SI Logic              | 99  |

|-----------------------|-----|

| ational Semiconductor | 99  |

| EC                    | 100 |

| iemens                | 100 |

| GS-Thomson            | 100 |

| oshiba                | 100 |

| roduct Routing        | 101 |

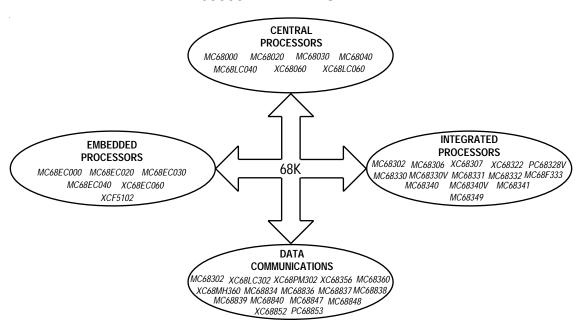

# M68000 FAMILY STRATEGY

The M68000 Family is already the industry standard in computing and embedded control applications.

#### Markets:

- Low- to Mid-Range Computing

- Laptop and Hand-Held Computing

- Telecommunications (Digital Switches, SDH Platforms, PABX)

- Office Automation (Printers, Faxes, Servers, X-Terminals)

- Network Controllers

- Consumer Products

The M68000 Family provides industry-standard architecture in an extremely cost-effective package/solution. Solutions are available from less than \$3 and to more than 100 MIPS with an excellent migration path.

#### M68000 FAMILY ROADMAP

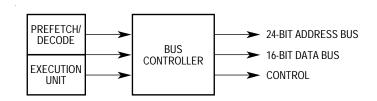

# MC68000

#### Features:

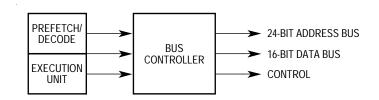

- 24-Bit Address Bus, 16-Bit Data Bus

- 16 32-Bit Registers

- 7 Interrupt Levels

# **Target Markets/Applications:**

Not recommended for new designs.

Orders will be accepted until December 1, 1995 and shipped through May 1996. After that date, the 68000 will no longer be available but replaced by the pin compatible CMOS 68HC000. Also see MC68EC000, MC68306, and 68307.

# **Competitive Advantages:**

8086–8088—Similar performance but limited migration path to higher performance Microprocessors

#### **Alternative Source:**

Hitachi, Signetics, SGS-Thomson

#### Literature:

| Title                                | Order Number      |

|--------------------------------------|-------------------|

| MC68000 Technical Summary            | MC68000/D         |

| M68000 User's Manual                 | M68000UM/AD Rev 8 |

| M68000 Programmer's Reference Manual | M68000PM/AD       |

| 68000 Microprocessor Family          | BR1115/D          |

## **Support Tools:**

M68EC000IDP—Integrated Development Platform: hardware/software evaluation module Third party support listed in *The 68K Source,* 1994 Edition, BR729/D.

# **Support Chips:**

MC68440/450—DMA Controllers MC68901—Multi-function Peripheral MC68230—Parallel Interface Timer MC68681—DUART

# Package/Speed Options:

| Device  | Package        | Speed     | Rev | Temperature    | Orde | er Qua | ntity | For Sample Order  |  |

|---------|----------------|-----------|-----|----------------|------|--------|-------|-------------------|--|

| Device  | rackage        | Speed     | VeA | ev remperature |      | MPQ    | POQ   | 1 or cample order |  |

| MC68000 | 64-Lead L*     | 8, 10, 12 | _   | _              | 6    | 6      | 216   |                   |  |

|         | 64-Lead P      | 8, 10, 12 | _   | _              | 6    | 6      | 192   |                   |  |

|         | 68-Lead R, RC* | 8, 10, 12 | _   | _              | 0    | 21     | 210   | SPAK000RCXX       |  |

|         | 68-Lead FN     | 8, 10, 12 | _   | _              | 0    | 18     | 1008  | SPAK000FNXX       |  |

MPQ =

Minimum Package Quantity

POQ = Preferred Order Quantity

SOQ = Sample Order Quantity

NOTE: FN = Plastic Leaded Chip Carrier (PLCC)

L = Ceramic DIP

P = Plastic Dual-In-Line Pin (PDIP)

R = Pin Grid Array (PGA)

RC = Pin Grid Array (PGA), Gold Lead Finish

# **History**

| Mask  | Rev | Shrink | Fab  | Geo  | Status     | Errata | PCN | Comments                          |

|-------|-----|--------|------|------|------------|--------|-----|-----------------------------------|

| C91E  | 4   | 30%    | MOS5 | 2.5μ | Production | _      | _   | Elimination of CFC processing     |

| C91E  | 3   | 30%    | MOS5 | 2.5μ | Canceled   | _      | _   | Never released to production      |

| C91E  | 2   | 30%    | MOS5 | 2.5μ | Production | _      | _   | Conversion of MOS5 to 5" line     |

| B26M  | 4   | 30%    | MOS5 | 2.5μ | Canceled   | _      | _   | Improved yield/speed (220 × 227)  |

| A72E  | 3   | 20%    | MOS5 | 2.8μ | Canceled   | _      | _   | Improved mask quality (230 × 260) |

| A72E  | 2   | 20%    | MOS5 | _    | Canceled   | _      | _   | AS noise reduction, split ground  |

| A72E  | 1   | 20%    | MOS5 | _    | Canceled   | _      | _   | Stress relief                     |

| A72E  | 0   | 20%    | MOS5 | _    | Canceled   | _      | _   | Add long fix                      |

| A74J  | _   | 10%    | MOS5 | _    | Canceled   | _      | _   |                                   |

| A92K  | _   | 10%    | MOS3 | _    | Canceled   | _      | _   |                                   |

| NK8   | _   | _      | _    | _    | _          | _      | _   |                                   |

| 18GN7 | _   | 10%    | MOS5 | _    | Canceled   | _      | _   | (257 × 291) Hi-rel only           |

| 17GN7 | _   | 10%    | MOS5 | _    | Canceled   | _      | _   |                                   |

| 8GN7  | _   | 10%    |      |      | Canceled   | _      | _   | Hi-rel only                       |

| 7GN7  | _   | 10%    | _    | _    | Canceled   | _      | _   |                                   |

| CCI   | _   | 10%    | _    | _    | _          | _      | _   |                                   |

First Silicon: July 1979

MC Qualification Date: Sept 1979

**Die Size:** 204 × 227 @ 30% (C91E)

**Devices:** Sites = 68,000; Active = 37,000

<sup>\*</sup>Not recommended for new designs

# MC68EC000

#### Features:

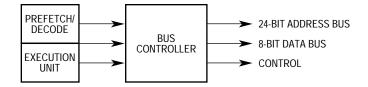

- 24-Bit Address Bus, 8-Bit or 16-Bit Data Bus

- 16 32-Bit Registers

- Interrupt Levels

- 2.7 MIPS Performance at 16.67 MHz

# **Target Markets/Applications:**

The 68EC000 represents the most inexpensive entry point to any 32-bit architecture. Upward migration to higher performance processors is possible because of software compatibility of the architecture. CMOS process ensures low power consumption. Target applications are PABX low level, line cards, GSM fax, modems, industrial control, instrumentation, etc. The 68EC000 is recommended for 8-bit applications that require higher performance and extended addressing range.

Also see MC68306 and 68307.

# **Competitive Advantages:**

Z80—Low cost but limited performance upgrade potential 8086/8088—Requires external support chips to avoid technical limitations

#### Literature

| Title                                | Order Number      |

|--------------------------------------|-------------------|

| MC68EC000 Technical Summary          | MC68EC000/D       |

| M68000 User's Manual                 | M68000UM/AD Rev 8 |

| M68000 Programmer's Reference Manual | M68000PM/AD       |

| 68EC0x0 Family Fact Brochure         | BR1109/D          |

#### **Support Tools:**

M68EC000IDP—Integrated Development Platform: hardware/software evaluation module Third party support listed in *The 68K Source*, 1994 Edition, BR729/D.

# **Support Chips:**

MC68901—Multi-function Peripheral MC68681—DUART

# Package/Speed Options:

| Device    | Package    | Speed             | Rev  | Rev Temp |     | er Qua | ntity | For Sample Order  |

|-----------|------------|-------------------|------|----------|-----|--------|-------|-------------------|

| Device    | rackage    | Speed             | IVEA | Temp     | SOQ | MPQ    | POQ   | i oi Sample Ordei |

| MC68EC000 | 68-Lead FN | 8, 10, 12, 16, 20 | _    | _        | 0   | 18     | 1008  | SPAKEC000FNXX     |

|           | 64-Lead FU | 8, 10, 12, 16, 20 | _    | _        | 0   | 84     | 840   | SPAKEC000FUXX     |

NOTE: FN = Plastic Leaded Chip Carrier (PLCC) MPQ = Minimum Package Quantity

FU = Plastic Quad Flat Pack (PQFP) POQ = Preferred Order Quantity

SOQ = Sample Order Quantity

# **History:**

| Mask  | Rev | Shrink | Fab    | Geo    | Status           | Errata | PCN | Comments                       |

|-------|-----|--------|--------|--------|------------------|--------|-----|--------------------------------|

| 1F30A | 1   | 78%    | MOS8   | 0.71μm | In Qualification | _      | _   | Changed contact sizing         |

| 0F30A | 0   | 78%    | MOS8   | 0.71μm | Canceled         | _      | _   | Die shrink, die size 130 × 143 |

| 0F86C | 0   | 63%    | Tohoku | 1.2μ   | Production       | _      | _   | Die size = 213.4 × 237.4       |

| 1F90A | 1   | 75%    | MOS8   | 0.8μ   | Production       | _      | _   | Changed polyimide reticle      |

| 0F90A | 0   | 75%    | MOS8   | .8μ    | Canceled         | _      | _   | Die shrink                     |

| 5C71T | 2   | 70%    | MOS8   | 1.0μ   | Canceled         | _      | _   |                                |

First Silicon: 3Q91

MC Qualification Date: 4Q91

**Die Size:**  $146 \times 162$  (F90A),  $213 \times 237$  (F86C),  $130 \times 143$  (F30A)

**Devices:** Sites = 68,000; Active = 37,000

# MC68HC000

#### Features:

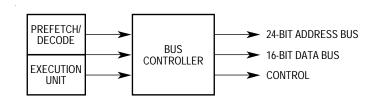

- 24-Bit Address Bus, 16-Bit Data Bus

- 16 32-Bit Registers

- 7 Interrupt Levels

- 2.7 MIPS Performance at 16 MHz

# **Target Markets/Applications:**

The 68HC000 processor is a low-power dissipation HCMOS version of the MC68000 16/32-bit microprocessor. It is completely pin, timing, parameter and code compatible with the standard (HMOS) MC68000. The 68HC000 offers power consumption lower by an order of magnitude than that for the HMOS 68000. Worst case power dissipations are: 0.131W @ 8 MHz, 0.158 W @ 10 MHz, 0.184 W @ 12.5 MHz, 0.263W @ 16.67 MHz.

The 64-pin P version is not sold in the United States.

#### **Competitive Advantages:**

8086/8088—Similar performance but limited migration path to higher performance Microprocessors

#### **Alternative Sources:**

Hitachi, Toshiba

#### Literature:

| Title                       | Order Number      |

|-----------------------------|-------------------|

| MC68HC000 Technical Summary | MC68HC000/D Rev 4 |

| M68000 User's Manual        | M68000UM/AD Rev 9 |

# **Support Tools:**

M68EC000IDP—Integrated Development Platform: hardware/software evaluation module Third party support listed in *The 68K Source*, 1994 Edition, BR729/D.

# **Support Chips:**

MC68901—Multi-function Peripheral MC68681—DUART

# Package/Speed Options:

| Device    | Package         | Speed             | Rev | Temp          | Orde | er Qua | ntity | For Sample Order |

|-----------|-----------------|-------------------|-----|---------------|------|--------|-------|------------------|

| Device    | rackage         | Speed             | Kev | Kev Tellip    |      | MPQ    | POQ   | For Sample Order |

| MC68HC000 | 64-Lead P       | 8, 10, 12, 16     | _   | _             | 6    | 6      | 192   | SPAKHC000PXX     |

|           | 68-Lead R*, RC* | 8, 10, 12, 16     | _   | CRC8,10,12,16 | 0    | 21     | 210   | SPAKHC000RCXX    |

|           | 68-Lead FN      | 8, 10, 12, 16, 20 | _   | CFN8,10,12,16 | 0    | 18     | 1008  | SPAKHC000FNXX    |

|           | 68-Lead FC*     | 8, 10, 12, 16     | _   | CFC8,10,16    | 0    | 78     | 780   | SPAKHC000FCXX    |

NOTE: FC = Plastic Quad Flat Pack (PQFP)

MPQ = Minimum Package Quantity POQ = Preferred Order Quantity

FN = Plastic Leaded Chip Carrier (PLCC) P = Plastic Dual-In-Line Pin (PDIP)

SOQ = Sample Order Quantity

R = Pin Grid Array (PGA)

RC = Pin Grid Array (PGA), Gold Lead Finish

# **History**

| Mask  | Rev | Shrink | Fab    | Geo  | Status           | Errata | PCN | Comments                                  |

|-------|-----|--------|--------|------|------------------|--------|-----|-------------------------------------------|

| 0G54B | 0   | 75%    | MOS11  | 0.8μ | In Qualification | _      | _   | MOS11 version of E72N - 147.1 x 162.1     |

| 2E60R | 2   | 63%    | Tohoku | 1.2μ | Production       | _      | _   |                                           |

| 1E60R | 1   | 63%    | Tohoku | 1.2μ | Canceled         | _      | _   |                                           |

| 0E60R | 0   | 63%    | Tohoku | 1.2μ | Canceled         | _      | _   | Die shrink, 212.6 × 236.6                 |

| 1E72N | 1   | 75%    | MOS8   | 0.8μ | Production       | _      | _   | Die shrink 147.1 × 163.2                  |

| 4C71T | 4   | 70%    | MOS8   | 1.0μ | Canceled         | _      | _   | Used on DIP and ext tempo versions        |

| 2B89N | 2   | 56%    | Tohoku | 1.5μ | Canceled         | _      | _   | Utilizes a differentially sized poly mask |

| 1C71T | 1   | 70%    | MOS8   | 1.0μ | Canceled         | _      | _   | Die size = 201 × 220                      |

| 3C44C | 3   | 0      | MOS8   | _    | Canceled         | _      | _   | 1.2μ process in MOS8                      |

| 1B89N | 1   | 56%    | Tohoku | 1.5μ | Canceled         | _      | _   | Die size = 242 × 271                      |

| 1B66R | 1   | 20%    | MOS8   | _    | Canceled         | _      | _   | Shrink and fix latch up problem           |

| 2C44C | 2   | 0      | MOS8   | _    | Canceled         | _      | _   | Poly sizing change for speed improvement  |

| 1C44C | 1   | 0      | MOS8   | _    | Canceled         | _      | _   | Fix latch up problem                      |

| 4B12C | 3   | 0      | MOS8   | _    | Canceled         | _      | _   | Poly sizing change for yield enhancement  |

| 3B12C | 2   | 0      | MOS8   | _    | _                | _      | _   | Speed path fix for speed enhancement      |

| 1B12C | 1   | 0      | MOS8   | _    | Canceled         | _      | _   | Poly layer sized for speed enhancement    |

| 0B12C | 0   | 0      | MOS8   | _    | Canceled         | _      | _   | Original Motorola mask set                |

First Silicon: Aug 1986 MC Qualification Date: 4Q86

Die Size:  $147.1 \times 163.2$  (E72N),  $147.1 \times 162.1$  (0G54B),

$213 \times 237 \text{ (E60R)}$

Devices: Sites = 68,000; Active = 42,000

<sup>\*</sup> Not recommended for new designs

# MC68HC001

#### Features:

- 24-Bit Address Bus, 16-Bit Data Bus

- 16 32-Bit Registers

- 7 Interrupt Levels

- 2.7 MIPS Performance at 16 MHz

# **Target Markets/Applications:**

The 68HC001 is functionally and software compatible with the 68HC000. In addition, the 68HC001 features a mode function which allows the processor to operate as a 16-bit 68000 or an 8-bit 68008.

MC68HC001 will be discontinued in 1995. The 68HC001 8-bit functionality will be incorporated into the 68HC000.

## Literature:

| Title                         | Order Number      |

|-------------------------------|-------------------|

| MC68HC001/D Technical Summary | MC68HC001/D Rev 4 |

| M68000 User's Manual          | M68000UM/AD Rev 8 |

## **Support Tools:**

M68EC000IDP—Integrated Development Platform: hardware/software evaluation module Third party support listed in *The 68K Source,* 1994 Edition, BR729/D.

# **Support Chips:**

MC68901—Multi-function Peripheral MC68681—DUART MC68HC05I8—MCU

# Package/Speed Options:

| Device     | Package     | Speed         | Rev | Tomp          | Orde | er Qua | ntity | For Sample Order |

|------------|-------------|---------------|-----|---------------|------|--------|-------|------------------|

| Device     | Fackage     | Speed         | VeA | Rev Temp      |      | MPQ    | POQ   | Tor Sample Order |

| MC68HC001* | 68-Lead FC* | 8, 10, 12, 16 | _   | _             | 0    | 78     | 780   | SPAKHC001FCXX    |

|            | 68-Lead FN* | 8, 10, 12, 16 | _   | CFN8,10,12,16 | 0    | 18     | 1008  | SPAKHC001FNXX    |

|            | 68-Lead RC* | 8, 10, 12, 16 | _   | CRC8,10,12,16 | 0    | 21     | 210   | SPAKHC001RCXX    |

NOTE: FC = Plastic Quad Flat Pack (PQFP) MPQ = Minimum Package Quantity FN = Plastic Leaded Chip Carrier (PLCC) POQ = Preferred Order Quantity

RC = Pin Grid Array (PGA), Gold Lead Finish SOQ = Sample Order Quantity

\*No new designs.

# **History**

| Mask  | Rev | Shrink | Fab    | Geo  | Status           | Errata | PCN | Comments                  |

|-------|-----|--------|--------|------|------------------|--------|-----|---------------------------|

| 2E60R | 2   | 63%    | Tohoku | 1.2μ | Production       | _      | _   |                           |

| 1E60R | 1   | 63%    | Tohoku | 1.2μ | Canceled         | _      | _   |                           |

| 0E60R | 0   | 63%    | Tohoku | 1.2μ | Canceled         | _      | _   | Die shrink, 212.6 × 236.6 |

| 1E72N | 1   | 75%    | MOS8   | 0.8μ | Production       | _      | _   | Die shrink 147.1 × 163.2  |

| 4C71T | 4   | 70%    | MOS8   | 1.0μ | Canceled         | _      | _   |                           |

| 1C71T | 1   | 70%    | MOS8   | 1.0μ | Canceled         | _      | _   | Die size = 201 × 220      |

| 2C72P | 2   | 56%    | MOS8   | 1.5μ | Canceled         | _      | _   | Downsized PO5 by .22μm    |

| 1C72P | 1   | 56%    | MOS8   | 1.5μ | Canceled         | _      | _   | Increased bus speed       |

| C72P  | 0   | 56%    | MOS8   | 1.5μ | Canceled         | _      | _   | Die size = 242 × 270      |

| 0G54B | 0   | 75%    | MOS11  | 0.8μ | In Qualification | _      | _   | MOS11 version of E72N     |

First Silicon: 4Q89 MC Qualification Date: 4Q89

**Die Size:**  $147.1 \times 162.1 \text{ (0G54B)}, 147.1 \times 163.2 \text{ (E72N)},$

213 × 237 (E60R)

**Devices:** Sites = 68,000; Active = 42,000

# MC68008

#### Features:

- 8-Bit Data Bus

- 16 32-Bit Data and Address Registers

- 14 Addressing Modes

- Complete Compatability with the MC68000

# **Target Markets/Applications:**

Not recommended for new designs.

Orders will be accepted until December 1, 1995 and shipped through May 1996. After that date, the 68008 will only be available from SGS-Thomson. The LC version was discontinued in March, 1992.

The 68008 has the same register set, same instructions, and same functionality as the 68000. The major differences between the 68000 and 68008 are that the 68008 has an 8-bit data bus, it can only address up to 4 megabytes of memory (PLCC), and it has a two wire bus arbitration scheme.

#### Literature:

| Title                        | Order Number |

|------------------------------|--------------|

| Minimum System Configuration | AN897/D      |

| M68008 Technical Summary     | BR259/D      |

| M68000 User's Manual Rev 8   | M68000UM/AD  |

## **Support Tools:**

Third party support listed in *The 68K Source*, 1994 Edition, BR729/D.

## **Support Chips:**

No longer available

# Package/Speed Options:

| Device  | Package    | Speed | Rev | Temp   | Orde | er Qua | ntity | For Sample Order  |

|---------|------------|-------|-----|--------|------|--------|-------|-------------------|

| Device  | Fackage    | Speed | Kev | Tellip | SOQ  | MPQ    | POQ   | 1 or Sample Order |

| MC68008 | 52-Lead FN | 8, 10 | _   | _      | 0    | 23     | 1955  | SPAK008FN         |

|         | 48-Lead P  | 8, 10 | _   | _      | 7    | 7      | 294   |                   |

NOTE: FN = Plastic Leaded Chip Carrier (PLCC)

P = Plastic Dual-In-Line Pin (PDIP)

MPQ = Minimum Package Quantity POQ = Preferred Order Quantity

SOQ = Sample Order Quantity

# History

| Mask | Rev | Shrink | Fab  | Geo  | Status     | Errata | PCN | Comments                      |

|------|-----|--------|------|------|------------|--------|-----|-------------------------------|

| C88P | 1   | 30%    | MOS5 | 2.5μ | Production | _      | _   | Elimination of CFC processing |

| C88P | 0   | 30%    | MOS5 | 2.5μ | Canceled   | _      | _   | 5" wafer conversion           |

| PR4  | 0   | 20%    | MOS5 | _    | Canceled   | _      | _   | Logic fix, radial die         |

First Silicon: 2Q82

MC Qualification Date: 1Q83

**Die Size:**  $230 \times 209$

**Devices:** Sites = 70,000; Active = 36,750

# MC68010

#### Features:

- 16 32-Bit Data and Address Registers

- 16 Mbyte Direct Addressing Range

- Virtual Memory, Machine Support

- 24-Bit Address Bus, 16-Bit Data Bus

# **Target Markets/Applications:**

Not recommended for new designs.

Orders will be accepted until December 1, 1995 and shipped through May 1996. After that date, the 68010 will no longer be available. The LC version was discontinued in March, 1992.

The 68010 is pin-for-pin compatible with the 68000 and has all the features of the 68000 plus faster instruction execution, virtual memory operation, vector base register, and automatic "loop mode".

#### Literature:

| Title                    | Order Number      |

|--------------------------|-------------------|

| M68000 User's Manual     | M68000UM/AD Rev 8 |

| M68010 Technical Summary | BR269/D           |

# **Support Tools:**

Third party support listed in *The 68K Source*, 1994 Edition, BR729/D.

# **Support Chips:**

No longer available

# Package/Speed Options:

| Device  | Packago         | Package Speed |     | Temp | Orde | er Qua | ntity | For Sample Order  |

|---------|-----------------|---------------|-----|------|------|--------|-------|-------------------|

| Device  | rackage         | Speeu         | Rev | remp | SOQ  | MPQ    | POQ   | 1 of Sample Order |

| MC68010 | 68-Lead FN*     | 8, 10, 12     | _   | _    | 0    | 19     | 1064  | SPAK010FNXX       |

|         | 64-Lead P*      | 8, 10, 12     | _   | _    | 6    | 6      | 192   |                   |

|         | 68-Lead R*, RC* | 8, 10, 12     | _   | _    | 0    | 21     | 210   | SPAK010RCXX       |

NOTE: FN = Plastic Leaded Chip Carrier (PLCC) MPQ = Minimum Package Quantity

P = Plastic Dual-In-Line Pin (PDIP) POQ = Preferred Order Quantity

R = Pin Grid Array (PGA( SOQ = Sample Order Quantity

RC = Pin Grid Array (PGA), Gold Lead Finish

# **History**

| Mask | Rev | Shrink | Fab  | Geo  | Status     | Errata | PCN | Comments                                   |

|------|-----|--------|------|------|------------|--------|-----|--------------------------------------------|

| C97R | 3   | 25%    | MOS5 | 2.6μ | Production |        |     | Resizing 01/05 layers                      |

| C97R | 2   | 25%    | MOS5 | 2.6μ | Canceled   | _      | _   | Elimination of CFC processing              |

| C97R | 1   | 25%    | MOS5 | 2.6μ | Canceled   | _      | _   | 5" wafer conversion                        |

| A71R | 0   | 25%    | MOS5 | 2.6μ | Canceled   | _      | _   | AS ring noise reduction, split ground ring |

| TA2  | 2   | 10%    | MOS5 | 3.2μ | Canceled   | _      | _   | Speed fix                                  |

| TA2  | 1   | 10%    | MOS5 | 3.2μ | Canceled   | _      | _   |                                            |

First Silicon: 3Q82 MC Qualification Date: 4Q82

**Die Size:** 237.5 × 270

**Devices:** Sites = 84,000; Active = 43,990

<sup>\*</sup> Not recommended for new designs

# MC68020

#### Features:

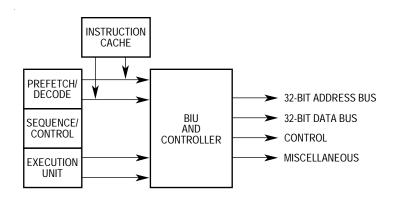

- 32-Bit Address Bus, 32-Bit Data Bus

- 256-Byte Instruction Cache

- Coprocessor Interface

- 9.8 MIPS/0.25MFLOPS Performance at 33 MHz

# **Target Markets/Applications:**

The 68020 is the first microprocessor to use a full 32-bit internal and external architecture and offers a vast increase in performance over 8- and 16-bit processors. The dynamic bus feature improves system flexibility, which allows use of 8- or 16-bit peripherals. The MC68EC020 should also be considered unless there is a clear need for a 32-bit address bus.

#### Literature:

| Title                                | Order Number |

|--------------------------------------|--------------|

| MC68020 Technical Summary (Rev 4)    | MC68020/D    |

| M68020 User's Manual                 | M68020UM/AD  |

| M68000 Programmer's Reference Manual | M68000PM/AD  |

## **Support Tools:**

M68EC020IDP—Integrated Development Platform: hardware/software evaluation module Third party support listed in *The 68K Source*, 1994 Edition, BR729/D.

# **Support Chips:**

MC68882—Enhanced Floating-Point Coprocessor

# Package/Speed Options:

| Device  | Package      | Speed             | Rev | Temp          | Orde | er Qua | ntity | For          |

|---------|--------------|-------------------|-----|---------------|------|--------|-------|--------------|

| Device  | rackaye      | Speed             | Kev | Temp          | SOQ  | MPQ    | POQ   | Sample Order |

| MC68020 | 114-Lead RC  | 12,16, 20, 25, 33 | Е   | CRC16, 20, 25 | 1    | 1      | 14    | MC68020RCXXE |

|         | 114-Lead RP  | 16, 20, 25        | Е   | CRP16         | 1    | 1      | 13    | MC68020RPXXE |

|         | 132-Lead FE* | 16, 20, 25, 33    | E   | _             | 2    | 36     | 180   | SPAK020FEXXE |

|         | 132-Lead FC  | 16, 20, 25, 33    | Е   | CFC16, 20, 25 | 2    | 36     | 360   | SPAK020FCXXE |

NOTE: FC = Plastic Quad Flat Pack (PQFP) MPQ = Minimum Package Quantity

FE = Ceramic Quad Flat Pack (CQFP) POQ = Preferred Order Quantity

RC = Pin Grid Array (PGA), Gold Lead Finish SOQ = Sample Order Quantity

RP = Plastic Pin Grid Array

# **History:**

| Mask  | Rev | Shrink | Fab    | Geo   | Status     | Errata | PCN | Comments                           |

|-------|-----|--------|--------|-------|------------|--------|-----|------------------------------------|

| C54S  | Α   | 67%    | MOS8   | 1.0μ  | Production | _      | _   | Military product only              |

| C10H  | Α   | 60%    | Tohoku | 1.2μ  | Production | _      | _   | Extended temperature only          |

| B69R  | В   | 60%    | APRDL  | 1.2μ  | Canceled   | _      | _   | 33 MHz - 60% shrink only           |

| B49N  | В   | 60%    | APRDL  | 1.2μ  | Canceled   | _      | _   | 33 MHz - 60% shrink only           |

| B47K  | В   | 50%    | MOS8   | 1.5μ  | Canceled   | _      | _   | Same as B87E but for NIKON stepper |

| B87E  | В   | 50%    | MOS8   | 1.5μ  | Canceled   | _      | _   | Internal rev. # change             |

| B40G  | Α   | 55%    | MOS8   | 1.35μ | Canceled   | _      | _   |                                    |

| 2A70N | _   | 40%    | MOS8   | 1.7μ  | Canceled   | _      | _   |                                    |

| 1A43S | _   | 50%    | MOS8   | 1.5μ  | Canceled   | _      | _   | Speed enhancement/cost reduction   |

| 2A45J | _   | 40%    | MOS8   | 1.7μ  | Canceled   | _      | _   | Phased out - March, 1986           |

| 1A45J | L   | 40%    | MOS8   | 1.7μ  | Canceled   | _      | _   | Phased out - March, 1986           |

| A45J  | K   | 40%    | MOS8   | 1.7μ  | Canceled   | _      | _   | Virtual bug                        |

| A23G  | J   | 40%    | MOS8   | 1.7μ  | Canceled   | _      | _   |                                    |

| A92E  | _   | 40%    | APRDL  | 1.7μ  | Canceled   | _      | _   |                                    |

| E30G  | Α   | 67%    | TSC    | 1.0μ  | Production |        | _   | Optical identical to C54S          |

First Silicon: May 1984

MC Qualification Date: 2Q85

**Die Size:**  $252 \times 244, 282 \times 276$

**Devices:** Sites = 190,000; Active = 103,000

<sup>\*</sup>Not recommended for new designs

# MC68EC020

#### Features:

- 24-Bit Address Bus, 32-Bit Data Bus

- 256-Byte Instruction Cache

- Coprocessor Interface

- 7.4 MIPS Performance at 25 MHz

# **Target Markets/Applications:**

The strategy behind the 68EC020 is to upgrade current 68000 and 68HC000 users to a higher performance product with minimum increase in device or system cost. Key applications are PABX low level, GSM basestations, network controllers, printers, dumb terminals, robotics, VME boards, instrumentation, etc. The MC68EC020 has a 24-bit address bus and does not support extended temperature.

## **Competitive Advantages:**

960SA—Similar price range, but overall system cost increased due to extra logic

960SB—On-chip floating point unit. Can be attacked with higher performance 68EC020/68882 combination at aggressive price

#### Literature:

| Title                                | Order Number |

|--------------------------------------|--------------|

| MC68EC020 Technical Summary          | MC68EC020/D  |

| M68020 User's Manual                 | M68020UM/AD  |

| M68000 Programmer's Reference Manual | M68000PM/AD  |

| 68EC0x0 Family Fact Brochure         | BR1109/D     |

## **Support Tools:**

M68EC020IDP—Integrated Development Platform: hardware/software evaluation module. Third party support listed in *The 68K Source*, 1994 Edition, BR729/D.

# **Support Chips:**

MC68882—Floating-Point Coprocessor MC68307—Slave Mode

# Package/Speed Options:

| Device    | Package     | Speed  | Rev Temp |           | Orde | er Qua | ntity | For           |

|-----------|-------------|--------|----------|-----------|------|--------|-------|---------------|

| Device    | rackage     | Speed  | IVEA     | Tellip    | SOQ  | MPQ    | POQ   | Sample Order  |

| MC68EC020 | 100-Lead FG | 16, 25 | _        | CFG16     | 2    | 66     | 264   | SPAKEC020FGXX |

|           | 100-Lead RP | 16, 25 | _        | CRP16, 25 | 1    | 1      | 13    | MC68EC020RPXX |

NOTE: FG = Plastic Quad Flat Pack (PQFP)

RP = Plastic Pin Grid Array

MPQ = Minimum Package Quantity

POQ = Preferred Order Quantity

SOQ = Sample Order Quantity

# **History:**

| Mask | Rev | Shrink | Fab    | Geo  | Status     | Errata | PCN | Comments                                 |

|------|-----|--------|--------|------|------------|--------|-----|------------------------------------------|

| E13G | Α   | 67%    | Tohoku | 1.0μ | Production | _      | _   | Optically identical to D76E              |

| D76E | Α   | 67%    | MOS8   | 1.0μ | Production | _      | _   |                                          |

| C10H | А   | 60%    | Tohoku | 1.2μ | Production | _      | _   | On RP package, has been replaced by E13G |

First Silicon: May 1991

MC Qualification Date: 2Q91

**Die Size:**  $239 \times 247$

**Devices:** Sites = 190,000; Active = 103,000

# MC68030

#### Features:

- 32-Bit Address Bus, 32-Bit Data Bus

- 256-Byte On-Chip Instruction Cache

- 256-Byte On-Chip Data Cache

- 17.9 MIPS at 50 MHz

- Burst Memory Interface

- Internal Harvard Architecture

- Dynamic Bus Sizing

- On-Chip Memory Management

# **Target Markets/Applications:**

The 68030 is well suited for all applications requiring moderate performance and low cost (via dynamic bus sizing, burst memory interface, etc.). Memory management support provides protection for users and tasks allowing controlled execution of programs. Target markets are high-speed LAN controllers (Ethernet, FDDI, X.25, etc.), I/O processors, laser printers, X-terminals, mid-range PCs, low-end workstations, servers, etc.

Principle markets include low-end to mid-range personal computers as well as embedded applications that require the protection features of a memory management unit.

#### **Competitive Advantages:**

Intel 386—Comparable 030 performance

Weaknesses—Has awkward register set and memory management

Intel 960KA—Comparable 68030 performance at approximately the same price range

Weaknesses—Multiplexed address and data buses. No data cache. Performance very

susceptible to wait states. Interrupt latency poor—Intel quote typically 1 ms at 33 MHz

#### Literature:

| Title                                | Order Number |

|--------------------------------------|--------------|

| MC68030 Technical Summary            | MC68030/D    |

| MC68030 User's Manual                | MC68030UM/AD |

| M68000 Programmer's Reference Manual | M68000PM/AD  |

| 68000 Microprocessor Family          | BR1115/D     |

# **Support Tools:**

M68EC030IDP—Integrated Development Platform: hardware/software evaluation module Third party support listed in *The 68K Source*, 1994 Edition, BR729/D.

# **Support Chips:**

MC68882—Floating-Point Coprocessor MC88915/MC88916—Clock Driver Crystals—Champion, Kyocera, ACT FSRAMS—MCM6206C, MCM6226A MC68307—Slave Mode

# Package/Speed Options:

| Device  | Package     | Speed             | Rev | Temp           | Orde | er Qua | ntity | For          |

|---------|-------------|-------------------|-----|----------------|------|--------|-------|--------------|

| Device  | rackage     | Speed             | VeA | remp           | SOQ  | MPQ    | POQ   | Sample Order |

| MC68030 | 128-Lead RC | 16,20,25,33,40,50 | С   | CRC16,20,25,33 | 1    | 1      | 14    |              |

|         | 124-Lead RP | 16,20,25,33       | С   | CRP16,20,25,33 | 1    | 1      | 13    |              |

|         | 132-Lead FE | 16,20,25,33       | С   | _              | 0    | 36     | 180   | SPAK030FEXXC |

NOTE: FE = Ceramic Quad Flat Pack (CQFP) MPQ = Minimum Package Quantity

RC = Pin Grid Array (PGA), Gold Lead Finish POQ = Preferred Order Quantity

RP = Plastic Pin Grid Array SOQ = Sample Order Quantity

#### **History:**

| Mask  | Rev | Shrink | Fab    | Geo   | Status     | Errata | PCN | Comments                               |

|-------|-----|--------|--------|-------|------------|--------|-----|----------------------------------------|

| C74N  | В   | 67%    | MOS8   | 1.0μ  | Production | No     | Yes | Process change                         |

| D62C  | В   | 60%    | Tohoku | 1.2μ  | Canceled   | No     | Yes | Tohoku die                             |

| D66C  | В   | 67%    | Tohoku | 1.0μ  | Production | No     | Yes | Tohoku die                             |

| F91C  | С   | 73%    | Tohoku | 0.8μ  | Production | No     | Yes | RC, FE package only                    |

| C48A  | G   | 60/67% | APRDL  | 1.2μ  | Canceled   | _      | _   | 33-MHz evaluation & bug fixer          |

| C43C  | В   | 60%    | MOS8   | 1.2μ  | Canceled   | No     | _   |                                        |

| B67R  | I   | 60%    | MOS8   | 1.2μ  | Canceled   | _      | _   | 33-MHz MOS8 process certification-C48A |

| 1B56P | D   | 55%    | APRDL  | 1.35μ | Canceled   | Yes    | _   | 25 MHz, 1 errata                       |

| 3B47B | С   | 55%    | APRDL  | 1.35μ | Canceled   | Yes    | _   | 2 Errata                               |

| B47B  | 0   | 55%    | APRDL  | 1.35μ | Canceled   | _      | _   | Internal evaluation                    |

First Silicon: April 1987

MC Qualification Date: 4Q87

**Die Size**:  $311 \times 276$  (C74N),  $305 \times 282$  (D66C),  $256 \times 238$  (F91C)

**Devices**: Sites = 273,000; Active = 186,000

# MC68EC030

#### Features:

- 32-Bit Address Bus, 32-Bit Data Bus

- 256-Byte On-Chip Instruction Cache

- 256-Byte On-Chip Data Cache

- 14.3 MIPS at 40 MHz

- · Burst Memory Interface

- Internal Harvard Architecture

- Bus Sizing

## **Target Markets/Applications:**

The 68EC030 is well suited for all mid-range embedded control applications that require moderate performance, low cost and the option of surface-mount packaging. Target markets are high-speed LAN controllers (Ethernet, FDDI, X.25, etc.), I/O processors, laser printers, X-terminals, etc.

# **Competitive Advantages:**

Intel 960KA—Around 68EC030 performance at roughly same price

Weaknesses: Multiplexed address and data buses. No data cache. Performance very susceptible to wait states. Interrupt latency poor—Intel quote *typically* 1 ms at 33 MHz.

AMD29000—Performance lies between 68EC030 and 68EC040 levels

Weaknesses: Lower performance with DRAMs in burst-mode and much more susceptible to wait states. Large register sets—not well suited to multi-tasking.

#### Literature:

| Title                                | Order Number   |

|--------------------------------------|----------------|

| MC68EC030 Technical Summary          | MC68EC030/D    |

| MC68EC030 User's Manual              | MC68EC030UM/AD |

| M68000 Programmer's Reference Manual | M68000PM/AD    |

| 68000 Microprocessor Family          | BR1115/D       |

# **Support Tools:**

M68EC030IDP—Integrated Development Platform: hardware/software evaluation module Third party support listed in *The 68K Source,* 1994 Edition, BR729/D.

# **Support Chips:**

MC68882—Floating-Point Coprocessor MC68307—Slave Mode MC88915/MC88916—Clock Driver FSRAMS—MCM6206C, MCM6226A Crystals—Champion, Kyocera, ACT

# Package/Speed Options:

| Device    | ice Package Speed Rev Temp |        | Orde | er Qua | ntity | For |     |                |

|-----------|----------------------------|--------|------|--------|-------|-----|-----|----------------|

| Device    | rackage                    | Speed  | Kev  | remp   | SOQ   | MPQ | POQ | Sample Order   |

| MC68EC030 | 124-Lead RP                | 25, 40 | С    | _      | 1     | 1   | 13  |                |

|           | 132-Lead FE                | 25, 40 | С    | _      | 0     | 36  | 180 | SPAKEC030FEXXC |

|           | 144-Lead PV                | 25     | С    | _      | _     | 300 | 300 |                |

NOTE: FE = Ceramic Quad Flat Pack (CQFP) MPQ = Minimum Package Quantity

PV = Thin Quad Flat Pack (TQFP) POQ = Preferred Order Quantity

RP = Plastic Pin Grid Array SOQ = Sample Order Quantity

# History:

| Mask | Rev | Shrink | Fab    | Geo  | Status     | Errata | PCN | Comments        |

|------|-----|--------|--------|------|------------|--------|-----|-----------------|

| C74N | В   | 67%    | MOS8   | 1.0μ | Production | No     | Yes |                 |

| D66C | В   | 67%    | Tohoku | 1.0μ | Production | No     | Yes | Tohoku die      |

| D62C | В   | 60%    | Tohoku | 1.2μ | Canceled   | No     | Yes | Tohoku die      |

| F91C | С   | 73%    | Tohoku | 0.8μ | Production | No     | Yes | FE package only |

First Silicon: 1Q91

MC Qualification Date: 1Q91

**Die Size:**  $311 \times 276$  (C74N);  $305 \times 282$  (D66C),  $256 \times 238$  (F91C)

**Devices:** Sites = 251,000; Active = 183,000

# MC68040

#### Features:

- 32-Bit Address Bus, 32-Bit Data Bus

- 4-Kbyte On-Chip Instruction Cache

- 4-Kbyte On-Chip Data Cache

- On-Chip Floating-Point Support

- 43.8 MIPS at 40 MHz

- 5.3 MFLOPS at 40 MHz

- Burst Memory Interface

- On-Chip Memory Management

# **Target Markets/Applications:**

The 68040 is well suited for all applications that require high-integer and floating-point performance while still retaining compatibility with the 68K architecture. Target markets include servers, X-terminals, graphics low-end workstations, high-performance embedded applications.

## **Competitive Advantages:**

Intel 486—Dominates PC-DOS market

Weaknesses: 25-MHz 68040 outperforms 50-MHz 486 in both Ingram Labs and *PC Week* benchmarks. Numerous clones confuse functional and performance issues.

IDT 3051/52—Aggressive pricing, high performance, surface mount

Weaknesses: Multiplexed bus requires external components. RISC machine intolerant of wait states. Limited range of development tools compared to 68K

AMD29030/35—Aggressive pricing, 4K/8K instruction cache

Weaknesses: No data cache. Very high bus usage. No support for multi-processor system

#### Literature:

| Title                                | Order Number      |

|--------------------------------------|-------------------|

| MC68040 Technical Summary            | MC68040/D         |

| M68040 User's Manual                 | M68040UM/AD Rev 1 |

| M68000 Programmer's Reference Manual | M68000PM/AD       |

| 68000 Microprocessor Family          | BR1115/D          |

# **Support Tools:**

M68EC040IDP—Integrated Development Platform: hardware/software evaluation module Third party support listed in *The 68K Source*, 1994 Edition, BR729/D.

# **Support Chips:**

MC68150—Dynamic Bus Sizer

MC68307—Slave Mode

MC88915/MC88916—Clock Driver

Crystals—Champion, Kyocera, ACT

FSRAMS—MCM62940 Burst Mode SRAM

# Package/Speed Options:

| Device  | Package     | Speed      | Pov      | Rev Temp |   | er Qua | ntity | For          |

|---------|-------------|------------|----------|----------|---|--------|-------|--------------|

| Device  | rackage     | Эреец      | IVEA     |          |   | MPQ    | POQ   | Sample Order |

| MC68040 | 179-Lead RC | 25,33, 40  | _        | _        | 1 | 1      | 10    |              |

|         | 184-Lead FE | 25, 33, 40 | <b>—</b> | _        | 0 | 24     | 96    | SPAK040FEXX  |

NOTE: FE = Ceramic Quad Flat Pack (CQFP) MPQ = Minimum Package Quantity RC = Pin Grid Array (PGA), Gold Lead Finish POQ = Preferred Order Quantity

SOQ = Sample Order Quantity

## **History**

| Mask  | Rev | Shrink | Fab   | Geo   | Status     | Errata | PCN | Comments                                 |

|-------|-----|--------|-------|-------|------------|--------|-----|------------------------------------------|

| 2E42K | _   | 80%    | MOS11 | 0.65μ | Production | No     | Yes | See addendum to user's manual on AESOP   |

| 2E31F | М   | 80%    | MOS11 | 0.65μ | Canceled   | Yes    | Yes |                                          |

| OE31F | М   | 80%    | MOS11 | 0.65μ | Canceled   | Yes    | Yes |                                          |

| 7D98D | Е   | 75%    | MOS8  | 0.8μ  | Canceled   | Yes    | _   |                                          |

| D43B  | В   | 75%    | MOS8  | 0.8μ  | Canceled   | Yes    | _   |                                          |

| 4D50D | Α   | 75%    | MOS8  | 0.8μ  | Canceled   | Yes    | _   |                                          |

| 5D98D | Е   | 75%    | MOS8  | 0.8μ  | Canceled   | Yes    | Yes | 100 C test temperature only at this time |

| 9D50D | В   | 75%    | MOS8  | 0.8μ  | Canceled   | Yes    | _   |                                          |

MC Qualification Date: 2Q95

**Die Size:**  $473 \times 500$

**Devices:** Sites = 1,170,000; Active = 844,000

# XC68040V

#### Features:

- Low Voltage (3.3v), Low Power (1.5 watts @ 33 MHz)

- Low-Power Mode for Full Power-Down Capatibility (660uW)

- Full Static Design

- Dual Input/Output Voltage Compatibility (3.3 V & 5 V TTL)

- Identical Code to the MC68040 plus LPSTOP Command for Power Down

- Non-Multiplexed 32-Bit Address Bus, 32-Bit Data Bus

- 4K-Byte On-Chip Instruction Cache

- 4K-Byte On-Chip Data Cache

- 26.1 MIPS Integer Performance at 25 MHz

- Burst Memory Interface

- On-Chip Memory Management Unit

# **Target Markets/Applications:**

The principle target for the MC68040V is for all high-performance, power-sensitive, general computing and embedded processing applications.

## **Competitive Advantages:**

Intel 960CA/F: Marketed as a RISC high-end solution

Weaknesses: High-Power consumption and less performance RISC machine intolerant of wait states, requires expensive high speed SRAM. Poor IDT 3051/52, 3081/3082: Aggressive pricing, high performance, surface mount

Weaknesses: Multiplexed bus requires external components. RISC machine intolerant of wait states, requires expensive high-speed SRAM. High-power consumption

AMD29030/35—Aggressive pricing, 4K/8K instruction cache

Weaknesses: No data cache. Very high bus usage. No support for multiprocessor system. RISC machine intolerant of wait states, requires expensive high-speed SRAM. High-power consumption

#### Literature:

| Title                                 | Order Number      |

|---------------------------------------|-------------------|

| MC68040 VT Product Brief              | MC68040V/D        |

| M68040 User's Manual                  | M68040UM/AD Rev 1 |

| M68000 Programmer's Reference Manual  | M68000PM/AD       |

| The 68K Source                        | BR729/D           |

| 3.3 Volt Logic and Interface Circuits | BR1407/D          |

# **Support Tools:**

M68EC040IDP—Integrated Development Platform: hardware/software evaluation module In-Circuit emulation—Applied Microsystems

Third party support listed in *The 68K Source*, 1994 Edition, BR729/D.

# Support Chips:

MC68150—Dynamic Bus Sizer MC88915/MC88916/MC8892—Clock Driver Crystals—Champion, Kyocera, ACT National NM27C6841 Burst EPROM FSRAMS—MCM62940 Burst Mode SRAM

# Package/Speed Options:

| Device   | Package     | Speed Rev |      | Temp | Orde | er Qua | ntity | For          |

|----------|-------------|-----------|------|------|------|--------|-------|--------------|

| Device   | rackage     | Speed     | IVEA | Temp | SOQ  | MPQ    | POQ   | Sample Order |

| XC68040V | 179-Lead RC | 25,33     | _    | _    | 0    | 1      | 0     |              |

|          | 184-Lead FE | 25, 33    | _    |      | 1    | 21     | 0     | SPAK040FEXXV |

NOTE: FE = Ceramic Quad Flat Pack (CQFP)

MPQ = Minimum Package Quantity RC = Pin Grid Array (PGA), Gold Lead Finish POQ = Preferred Order Quantity

SOQ = Sample Order Quantity

## **History:**

| Mask  | Rev | Shrink | Fab   | Geo    | Status   | Errata | PCN | Comments |

|-------|-----|--------|-------|--------|----------|--------|-----|----------|

| 0F54F | _   | 80%    | MOS11 | .5 TLM | Sampling | Yes    | No  |          |

| 6D33T | _   | 80%    | MOS11 | .5 TLM | Canceled | Yes    | No  |          |

MC Qualification Date: 2Q96

Die Size: **Devices:**

**Process:** .5μ TLM

# MC68EC/LC040

#### Features:

- 32-Bit Address Bus, 32-Bit Data Bus

- 4-Kbyte On-Chip Instruction Cache

- 4-Kbyte On-Chip Data Cache

- 27.4 MIPS at 25 MHz

- Burst Memory Interface

- On-Chip Memory Management on LC040 Only

## **Target Markets/Applications:**

The MC68EC/LC040 is well suited for all high-end embedded control applications that require high performance, low cost, and memory management.

# **Competitive Advantages:**

Intel 486SX: Lowest cost 486 entry point

Weaknesses: No acceptance outside of DOS compatible marketplace.

IDT 3051/52: Aggressive pricing, high performance, surface mount

Weaknesses: Multiplexed bus requires external components. RISC machine intolerant of wait states. Limited development tool support compared to 68K.

AMD29030/35: Aggressive pricing, 4K/8K instruction cache

Weaknesses: No data cache. Very high bus usage. No support for multi-processor system.

## Literature:

| Title                                | Order Number      |

|--------------------------------------|-------------------|

| MC68LC040 Technical Summary          | MC68LC040/D       |

| MC68EC040 Technical Summary          | MC68EC040/D       |

| M68040 User's Manual                 | M68040UM/AD Rev 1 |

| M68000 Programmer's Reference Manual | M68000PM/AD       |

| 68000 Microprocessor Family          | BR1115/D          |

# **Support Tools:**

M68EC040IDP—Integrated Development Platform: hardware/software evaluation module Third party support listed in *The 68K Source*, 1994 Edition, BR729/D.

# **Support Chips:**

68150—Dynamic Bus Sizer

MC68307—Slave Mode

MC68360—Integrated Communication Controller

MC88915/MC88916—Clock Driver

Crystals—Champion, Kyocera, ACT

FSRAMS—MCM62940 Burst Mode SRAM

# Package/Speed Options:

|   | Device    | Package     | Speed      | Rev | Temp   | Orde | er Qua | ntity | For Sample Order |

|---|-----------|-------------|------------|-----|--------|------|--------|-------|------------------|

|   | Device    | Fackage     | Speed      | VeA | Tellip | SOQ  | MPQ    | POQ   | For Sample Order |

| ĺ | MC68EC040 | 179-Lead RC | 20, 25, 33 | _   | _      | 1    | 1      | 10    |                  |

|   | MC68LC040 | 184-Lead FE | 20, 25, 33 | _   | _      | 0    | 24     | 96    | SPAKLC040FEXX    |

NOTE: FE = Ceramic Quad Flat Pack (CQFP) MPQ = Minimum Package Quantity RC = Pin Grid Array (PGA), Gold Lead Finish POQ = Preferred Order Quantity

SOQ = Sample Order Quantity

# **History**

| Mask  | Rev | Shrink | Fab   | Geo   | Status     | Errata | PCN | Comments                            |

|-------|-----|--------|-------|-------|------------|--------|-----|-------------------------------------|

| 2E71M | _   | 80%    | MOS11 | 0.65μ | Production | No     | Yes | See Addendum User's Manual on AESOP |

| 2E23G | В   | 80%    | MOS11 | 0.65μ | Canceled   | Yes    | _   | XC orders supplied in 2E23G         |

| D39H  | Α   | 75%    | MOS8  | 0.8μ  | Canceled   | Yes    | No  |                                     |

MC Qualification Date: 4Q95

**Die Size:**  $461.4 \times 431.6$  **Devices:** Sites = 777,092

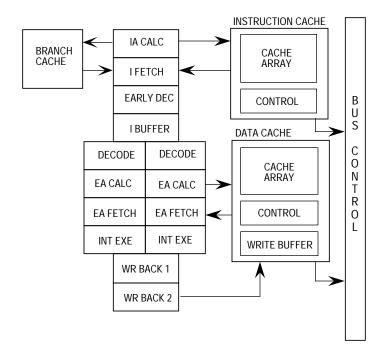

# XC68060

#### Features:

- Greater than 50 Integer SPECmarks at 50 MHz

- Dual Issue Execution Pipeline

- 32-Bit Address Bus, 32-Bit Data Bus

- 8-Kbyte On-Chip Instruction Cache

- 8-Kbyte On-Chip Data Cache

- 256-Entry Branch Cache

- On-Chip Floating-Point Support

- On-Chip Memory Management

- Burst Memory Interface

- Designed for Low Power

- 3.3 Volt Operation

## **Target Markets/Applications:**

The 68060 is well suited for all applications that require very high integer and floating-point performance while still retaining compatibility with the 68K architecture.

## **Competitive Advantages:**

Intel Pentium: Dominates PC-DOS market

Weaknesses: Requires 64-bit bus.

68060: Superior integer performance with low-cost memory system

#### Literature:

| Title                  | Order Number   |

|------------------------|----------------|

| MC68060 Product Brief  | MC68060/D      |

| M68060 User's Manual   | M68060UM/AD    |

| M68000 Family Brochure | BR1115/D Rev 1 |

| M68060 Family Brochure | BR1153/D       |

# **Support Tools:**

M68060IDP—Integrated Development Platform: hardware/software evaluation module. Available 2Q95.

# **Support Chips:**

MC68150—Dynamic Bus Sizer

MC88926—Clock Driver

Crystals—Champion, Kyocera, ACT

FSRAMS—MCM62940 Burst Mode SRAM

# Package/Speed Options:

| Device  | Package     | Speed      | Rev | Temp       | Orde | er Qua | ntity | For Sample Order |

|---------|-------------|------------|-----|------------|------|--------|-------|------------------|

| Device  | Fackage     | kage Speed |     | Kev Tellip |      | MPQ    | POQ   | For Sample Order |

| XC68060 | 206-Lead RC | 50         | _   | _          | 1    | 1      | 10    |                  |

NOTE: RC = Pin Grid Array (PGA), Gold Lead Finish MPQ = Minimum Package Quantity

POQ = Preferred Order Quantity SOQ = Sample Order Quantity

# **History**

| Mask  | Rev | Shrink | Fab   | Geo  | Status     | Errata | PCN | Comments |

|-------|-----|--------|-------|------|------------|--------|-----|----------|

| 1F43G | С   | 85%    | MOS11 | 0.5μ | Production | Yes    | _   |          |

| 0F43G | В   | 85%    | MOS11 | 0.5μ | Canceled   | Yes    | _   |          |

| D11W  | Α   | 85%    | APRDL | 0.5μ | Canceled   | Yes    | _   |          |

First Silicon: Dec 1993

XC Qualification Date: 1Q95

**Die Size:**  $582 \times 579$

**Devices:** Active = 2,530,000

### XC68EC060

#### Features:

- Greater than 50 Integer SPECmarks at 50 MHz

- Dual-Issue Execution Pipeline

- 32-Bit Address Bus, 32-Bit Data Bus

- 8-Kbyte On-Chip Instruction Cache

- 8-Kbyte On-Chip Data Cache

- 256-Entry Branch Cache

- Burst Memory Interface

- Designed for Low Power

- 3.3 Volt Operation

### **Target Markets/Applications:**

The 68EC060 is suited for high-end embedded control applications that require high performance low cost. Target markets include high-speed LAN controllers (Ethernet, FDDI, X.25, etc.), I/O processors, laser printers, X-terminals, routers, bridges, etc.

### **Competitive Advantages:**

Intel Pentium: Dominates PC-DOS market

Weaknesses: Requires 64-bit bus.

68060: Superior integer performance with low-cost memory system

### Literature:

| Title                  | Order Number |

|------------------------|--------------|

| MC68060 Product Brief  | MC68060/D    |

| M68060 User's Manual   | M68060UM/AD  |

| M68060 Family Brochure | BR1153/D     |

# **Support Tools:**

M68060IDP—Integrated Development Platform: hardware/software evaluation module. Available 2Q95.

# **Support Chips:**

MC68150—Dynamic Bus Size

MC88926—Clock Driver

Crystals—Champion, Kyocera, ACT

FSRAMS—MCM62940 Burst Mode SRAM

## Package/Speed Options:

| Device    | Package     | Speed | Rev  | Temp | Order Quantity |     | ntity | For Sample Order  |

|-----------|-------------|-------|------|------|----------------|-----|-------|-------------------|

| Device    | rackage     | Speed | IVEA | Temp | SOQ            | MPQ | POQ   | i oi Sample Order |

| XC68EC060 | 206-Lead RC | 50    | С    | _    | 1              | 1   | 10    |                   |

NOTE: RC = Pin Grid Array (PGA), Gold Lead finish MPQ = Minimum Package Quantity

POQ = Preferred Order Quantity SOQ = Sample Order Quantity

# **History**

| Mask  | Rev | Shrink | Fab   | Geo  | Status     | Errata | PCN | Comments                                 |

|-------|-----|--------|-------|------|------------|--------|-----|------------------------------------------|

| 1F43G | С   | 85%    | MOS11 | 0.5μ | Production | Yes    | _   |                                          |

| 0F43G | В   | 85%    | MOS11 | 0.5μ | Canceled   | Yes    | _   |                                          |

| D11W  | Α   | 85%    | APRDL | 0.5μ | Canceled   | Yes    |     | EC060s temp. sourced from full '060 mask |

First Silicon: Dec 1993

XC Qualification Date: 1Q95

**Die Size:**  $582 \times 579$

**Devices:** Active = 2,530,000

Process: HCMOS

## XC68LC060

#### Features:

- Greater than 50 Integer SPECmarks at 50 MHz

- Dual-Issue Execution Pipeline

- 32-Bit Address Bus, 32-Bit Data Bus

- 8-Kbyte On-Chip Instruction Cache

- 8-Kbyte On-Chip Data Cache

- 256-Entry Branch Cache

- Burst Memory Interface

- On-Chip Memory Management

- Designed for Low Power

- 3.3 Volt Operation

### **Target Markets/Applications:**

The 68LC060 is well suited for all high-end embedded control applications that require high performance, low cost, and the function of memory management.

## **Competitive Advantages:**

Intel Pentium: Dominates PC-DOS market

Weaknesses: Requires 64-bit bus.

68060: Superior integer performance with low-cost memory system

### Literature:

| Title                  | Order Number |

|------------------------|--------------|

| MC68060 Product Brief  | MC68060/D    |

| M68060 User's Manual   | M68060UM/AD  |

| M68060 Family Brochure | BR1153/D     |

# **Support Tools:**

M68060IDP—Integrated Development Platform: hardware/software evaluation module. Available 2Q95.

# **Support Chips:**

MC68150—Dynamic Bus Sizer

MC88926—Clock Driver

Crystals—Champion, Kyocera, ACT

FSRAMS—MCM62940 Burst Mode SRAM

# Package/Speed Options:

| Device    | Package     | Speed  | Rev  | Temp | Order Quantity |     | ntity | For Sample Order |  |

|-----------|-------------|--------|------|------|----------------|-----|-------|------------------|--|

| Device    | rackage     | Speeu  | IVEA | Temp | SOQ            | MPQ | POQ   | For Sample Order |  |

| XC68LC060 | 206-Lead RC | 50, 66 | _    | _    | 1              | 1   | 10    |                  |  |

NOTE: RC = Pin Grid Array (PGA), Gold Lead finish MPQ = Minimum Package Quantity

POQ = Preferred Order Quantity SOQ = Sample Order Quantity

## **History**

| Mask  | Rev | Shrink | Fab   | Geo  | Status     | Errata | PCN | Comments                                |

|-------|-----|--------|-------|------|------------|--------|-----|-----------------------------------------|

| 1F43G | С   | 85%    | MOS11 | 0.5μ | Production | Yes    | _   |                                         |

| 0F43G | В   | 85%    | MOS11 | 0.5μ | Canceled   | Yes    | _   |                                         |

| D11W  | Α   | 85%    | APRDL | 0.5μ | Canceled   | Yes    |     | LC060s temp. sourced from full 060 mask |

First Silicon: Dec 1993

XC Qualification Date: 1Q95

**Die Size:**  $582 \times 579$

**Devices:** Active = 2,530,000

Process: HCMOS

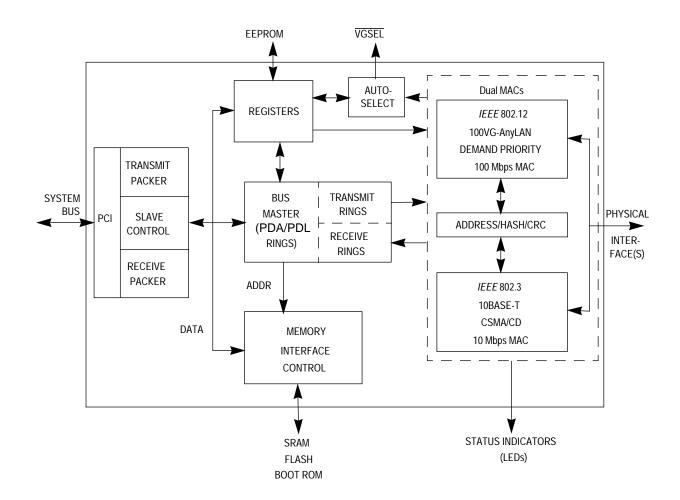

### XC68852 PCI MASTER INTERFACE

#### Features:

- IEEE 802.12 100VG AnyLAN Media Access Control Specification

- -Enables 100-Mbps Transmission over UTP, STP and Fiber

- —Supports Token Ring and Ethernet Formatted Packets

- —Supports Multimedia Applications with Two Levels of Priority

- Dual Media Access Controllers Included for 100VG-AnyLAN and 10BASE-T

- Integration of 10BASE-T Signals with the 100VG-AnyLAN MII Allows for Single Connector 10Mbps/100-Mbps Designs with Automatic Speed Detection

- 132-Mbytes Transfer Rate (PCI)

- Address Recognition of Broadcast, Multicast, and Station Addressed Packets

- LED Interface for Activity and Status Indicators

- 5-Volt Operation

### **Target Markets/Applications:**

The XC68852 fully implements the IEEE 802.12 100VG-AnyLAN standard and the IEEE 802.3 10BASE-T standard. This chip offers a high-integrated, high-performance, low-cost solution for 100 Mbps network adapter card applications. The 100VG-AnyLAN IEEE 802.12 standard supports all popular cable types, is a superset of Ethernet and Token Ring topologies, and provides guaranteed bandwidth for emerging applications such as multimedia

## **Competitive Advantages:**

TI—ThunderLAN chip (PCI only) is higher priced, but supports 10BASE-T, 100VG-AnyLAN and 100BASE-T.

#### Literature:

| Title                | Order Number |

|----------------------|--------------|

| M68852 Product Brief | MC68852/D    |

## Package/Speed Options:

| Device  | Package     | Speed | Rev  | Temp    | Order Quantity |     | ntity | For Sample Order   |  |

|---------|-------------|-------|------|---------|----------------|-----|-------|--------------------|--|

| Device  | rackage     | Speed | IVEA | Temp    | SOQ            | MPQ | POQ   | - For Sample Order |  |

| XC68852 | 160-Lead FT | 33    | _    | 0 to 70 | _              | _   | _     | SPAK852FT          |  |

NOTE: FT = Plastic Quad Flat Pack (PQFP)

MPQ = Minimum Package QuantityPOQ = Preferred Order QuantitySOQ = Sample Order Quantity

First Silicon: Sept 1995

MC Qualification Date: 2Q96

**Die Size:**  $306 \times 306$

Devices:

**Process:** .65μ TLM HCMOS

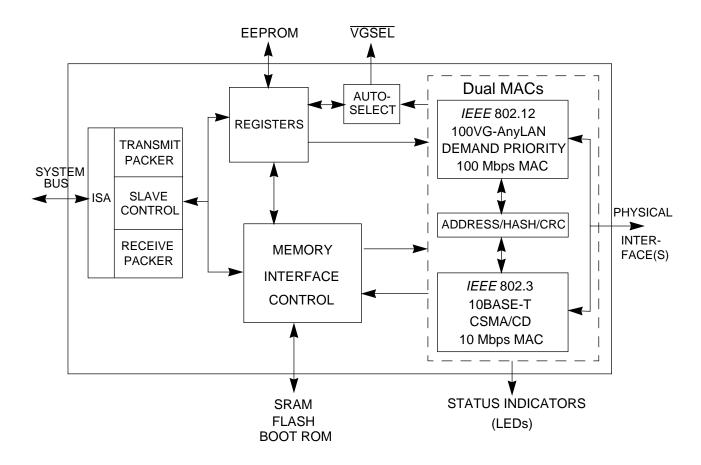

### PC68853 ISA SYSTEM INTERFACE

### Features:

- IEEE 802.12 100VG AnyLAN Media Access Control Specification

- —Enables 100 Mbps Transmission over UTP, STP and Fiber

- —Supports Token Ring and Ethernet Formatted Packets

- —Supports Multimedia Applications with Two Levels of Priority

- Dual Media Access Controllers Included for 100VG-AnyLAN and 10BASE-T

- Integration of 10BASE-T Signals with the 100VG-AnyLAN MII Allows for Single Connector 10Mbps/100-Mbps Designs with Automatic Speed Detection

- 8-Mbytes Transfer Rate (ISA)

- Address Recognition of Broadcast, Multicast, and Station Addressed Packets

- LED Interface for Activity and Status Indicators

- 5-Volt Operation

### **Target Markets/Applications:**

The PC68853 fully implements the IEEE 802.12 100VG-AnyLAN standard and the IEEE 802.3 10BASE-T standard. This chip offers a high-integrated, high-performance, low-cost solution for 100 Mbps network adapter card applications. The 100VG-AnyLAN IEEE 802.12 standard supports all popular cable types, is a superset of Ethernet and Token Ring topologies, and provides guaranteed bandwidth for emerging applications such as multimedia

## **Competitive Advantages:**

AT&T:—Poor support. Combined EISA/ISA chip is higher priced due to EISA overhead.

#### Literature:

| Title                | Order Number |

|----------------------|--------------|

| M68853 Product Brief | MC68853/D    |

# Package/Speed Options:

| Device  | Package     | Speed | Rev | Temp    | Order Quantity |     | ntity | For Sample Order   |  |

|---------|-------------|-------|-----|---------|----------------|-----|-------|--------------------|--|

| Device  | rackage     | Speed | VeA | Temp    | SOQ            | MPQ | POQ   | - For Sample Order |  |

| PC68853 | 144-Lead PV | 33    | _   | 0 to 70 | _              | _   | _     | SPAK853PV          |  |

NOTE: PV = Thin Quad Flat Pack (TQFP)

MPQ = Minimum Package Quantity

POQ = Preferred Order Quantity

SOQ = Sample Order Quantity

First Silicon: Nov 1995

MC Qualification Date: 2Q96

**Die Size:**  $204 \times 236$

Devices:

**Process:** .65μ TLM HCMOS

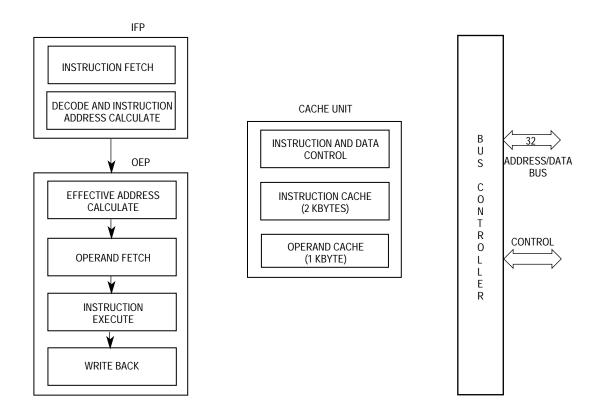

## XCF5102

#### Features:

- High Integer Performance

- —1 Instruction Per Clock Peak Performance

- Full Static Design Allows Operation Down to DC to Minimize Power Consumption

- On-Chip Caches

- -2K-bytes Instruction Cache

- —1K-bytes Data Cache

- 4 Separate Access Control Registers

- Simple Instruction Set Architecture

- —16 User Visible 32-Bit Wide Registers

- —User-mode Compatible with M68K Instruction Set

- —Supervisor / User Modes For System Protection

- —Vector Base Register To Relocate Exception Vector Table

- —Optimized For High Level Language Constructs

- Low Interrupt Latency

- Multiplexed 32-Bit Address and 32-Bit Data Bus To Minimize Board Space and Interconnections

- 3.3-Volt Operation

- 5-Volt TTL Compatible, 5-Volt CMOS Tolerant

- Three-State Pin

- Snoop

- JTAG IEEE 1149.1

- Single Bus Clock Input

- Fast Locking PLL

## **Target Markets/Applications:**

The XCF5102 is fully ColdFire code compatible. As the first chip in the ColdFire Family, it has been designed with special capabilities that allow it to also execute the M68000 code that exists today. These extensions to the Coldfire instruction set allow Motorola customers to utilize the XCF5102 as a bridge to future ColdFire processors for applications requiring the advantages of a variable-length RISC architecture. Compatibility with existing development tools such as compilers, debuggers, real-time operating systems and adapted hardware tools offers XCF5102 developers access to a broad range of mature tool support; enabling an accelerated product development cycle, lower development costs and critical time-to-market advantages for Motorola customers.

#### Literature:

| Title        | Order Number                                |

|--------------|---------------------------------------------|

| MCF5102UM/AD | MCF5102 User's Manual                       |

| M68000PM/AD  | M68000 Family Programmer's Reference Manual |

# Package/Speed Options:

| Device  | Package     | Speed      | Rev | Temp | Order Quantity |     | ntity | For Sample Order |

|---------|-------------|------------|-----|------|----------------|-----|-------|------------------|

| Device  | rackage     | Speed      | VeA | remp | SOQ            | MPQ | POQ   | For Sample Order |

| XCF5102 | 144-Lead PV | 16, 20, 25 | Α   | _    | 0              | 60  | 300   | SPAK5102PVXXA    |

NOTE: PV = Thin Quad Flat Pack (TQFP)

MPQ = Minimum Package Quantity

POQ = Preferred Order Quantity

SOQ = Sample Order Quantity

### M68300 FAMILY STRATEGY

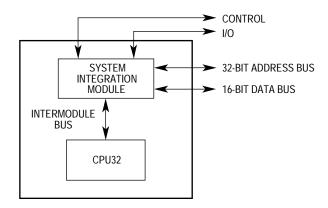

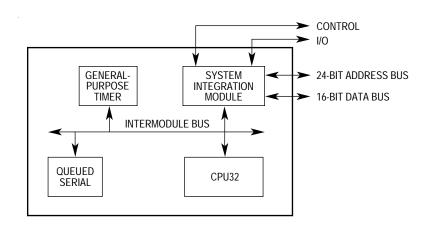

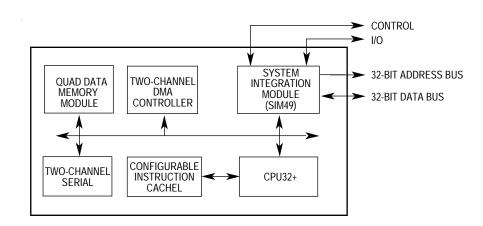

The M68300 Family consist of highly integrated processors aimed at the embedded computing and control market. The core processor is either the 68000 (MC68302, MC68306, MC68307, MC68322, MC68328) the CPU32 (MC68330, MC68340, MC68341), or the CPU32+ (MC68349, MC68360) which is a derivative of the MC68020.

The M68300 Family is the dominant 32-bit architecture in the area of integrated processors. This is achieved via the ongoing matching of Motorola capabilities to customer needs with particular focus in the following markets:

CONSUMER—CD-I, information terminals, global positioning (navigation aids) and personal computing.

COMMUNICATIONS—Network control and portable applications such as phones.

OFFICE EQUIPMENT—Copiers, network interfaces, portable computers and personal information computers.

AUTOMOTIVE—Engine and transmission management and navigation systems.

PORTABLE INSTRUMENTS—Measuring, monitoring, medical, inventory control, and computers.

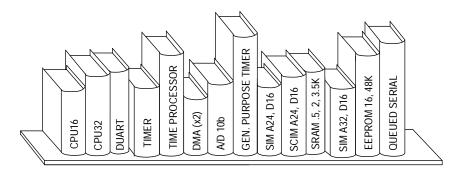

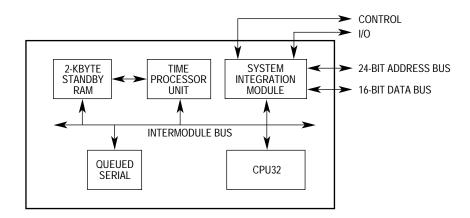

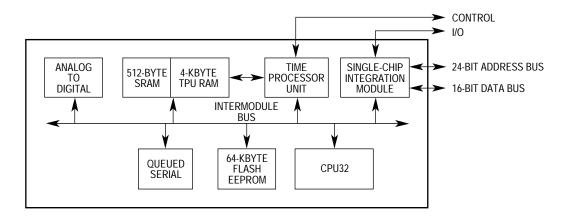

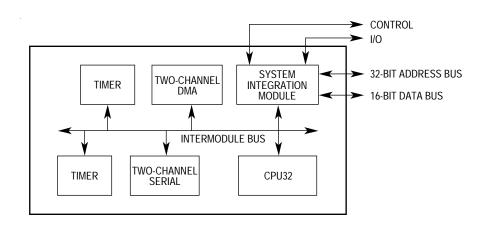

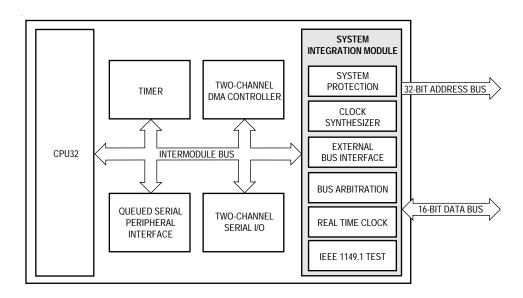

Much of the M68300 Family is based around the intermodule bus (IMB), which allows the device to be assembled from a library of peripheral modules as shown in the following illustration.

### PERIPHERAL LIBRARY

68300

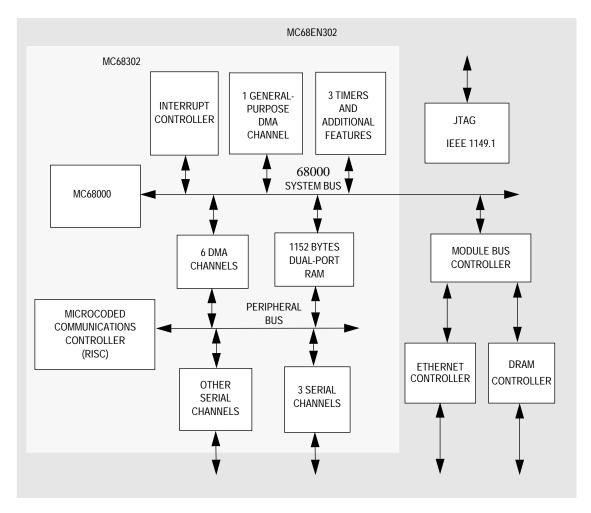

### MC68302

#### Features:

- 68000 Core Processor

- System Integration Block

- RISC Communications Processor

- 3 SCC's

- Slave Mode Option to Disable 68000

# **Target Markets/Applications:**

- Modems

- Computer I/O Subsystems

- Routers and Bridges

- Switching Networks

- ISDN

- Industrial Control

#### Literature:

| Title                                       | Order Number |

|---------------------------------------------|--------------|

| MC68302 User's Manual (Rev 2)               | MC68302UM/AD |

| MC68302 Technical Summary (Rev 2)           | MC68302/D    |

| MC68302 Development Tools Technical Summary | BR469/D      |

| M68300 Family Brochure (Rev 2)              | BR1114/D     |

## **Support Tools:**

MC68195 LocalTalk Adapter for the MC68302—The MC68195 interfaces the MC68302 to AppleTalk. Order as MC68195FN.

Third party support listed in *The 68K Source*, 1994 Edition, BR729/D.

# **Support Chips:**

M68302ADS—Application Development System M68302ADI—Host Interface Card M68302ICERC—PGA Target Cable

### Package/Speed Options:

#### Commercial Temperatures (0 to 70°C)

| Device  | rice Package Speed Rev Temp |            | Temp | Orde     | er Qua | ntity | For Sample Order |                  |

|---------|-----------------------------|------------|------|----------|--------|-------|------------------|------------------|

| Device  | Fackage                     | Speed      | VeA  | rev remp |        | MPQ   | POQ              | For Sample Order |

| MC68302 | 132-Lead RC                 | 16, 20, 25 | С    | _        | 1      | 1     | 14               |                  |

|         | 132-Lead FC                 | 16, 20, 25 | С    | _        | 0      | 36    | 144              | SPAK302FCXXC     |

|         | 144-Lead PV*                | 16, 20     | С    | _        | 0      | 60    | 300              | SPAK302PVXXC     |

NOTE: FC = Plastic Quad Flat Pack (PQFP) MPQ = Minimum Package Quantity

PV = Thin Quad Flat Pack (TQFP) POQ = Preferred Order Quantity

RC = Pin Grid Array (PGA), Gold Lead Finish SOQ = Sample Order Quantity

\*Available in 3.3V V<sub>CC</sub>

#### Industrial Temperatures (-40 to +85°C)

| Device     | Package       | Speed  | Rev | Temp      | Orde | er Qua | ntity | For Sample Order |

|------------|---------------|--------|-----|-----------|------|--------|-------|------------------|

| Device     | Fackage       | Speed  | VeA | Rev Temp  |      | MPQ    | POQ   | For Sample Order |

| MC68302CRC | 132-Lead PGA  | 16, 20 | С   | -40 to 85 | 0    | 1      | 14    |                  |

| MC68302CFC | 132-Lead PQFP | 16, 20 | С   | -40 to 85 | 0    | 36     | 144   | SPAK302CFCXXC    |

NOTE: CXX = Extended Temperatures

## **History**

| Mask  | Rev | Shrink | Fab   | Geo   | Status     | Errata | PCN                                     | Comments                |  |

|-------|-----|--------|-------|-------|------------|--------|-----------------------------------------|-------------------------|--|

| 1F26E | С   | _      | MOS11 | 0.65μ | Production | Yes    | Yes Yes Shrink; plastic package, cerami |                         |  |

| 1C65T | С   | _      | MOS8  | 0.8μ  | Canceled   | Yes    | Yes                                     | Shrink; ceramic package |  |

| 4B14M | В   | _      | MOS8  | 1.0μ  | Canceled   | Yes    |                                         | Double-layer metal      |  |

First Silicon: 2Q89 MC Qualification Date: 3Q89

**Die Size:**  $258 \times 251$

**Device:** Sites = 320,000; Active = 210,000

Process: CMOS

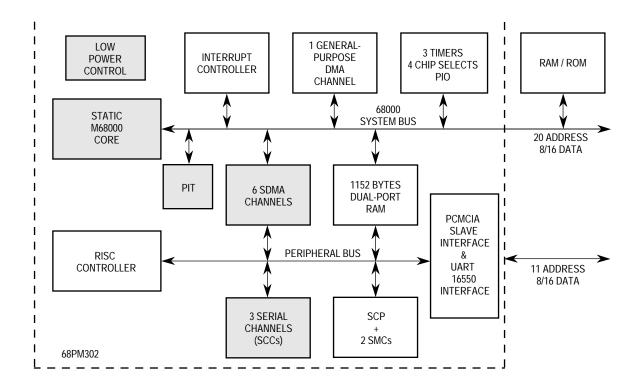

### XC68LC302

#### Features:

- 68EC000 Core CPU (16, 20, or 25 MHz)

- System Integration: 3 Timers Including a Watchdog, Independent DMA Controller, 1152

Bytes of Dual-Port Static RAM, 4 Chip Selects (CS), Interrupt Controller, Parallel Input/

Output (I/O) Ports, On-Chip Clock Generator with Output Signal, Periodic Interrupt Timer (PIT).

- Communications Processor: RISC-Based Communications controller, Serial Communication Channels Each Supporting HDLC/SDLC, UART, BISYNC, AUTOBAUD, and Transparent Modes, 4 Serial DMAs for the 2 SCCs, SCP for Synchronous Coummnications, Flexible Physical Interface Including IDL, NMSI, GCI, and PCM. Two Serial Management Controllers to Support IDL & GCI Auxiliary Channels.

- Available in Low Voltage (MC68LC302V)

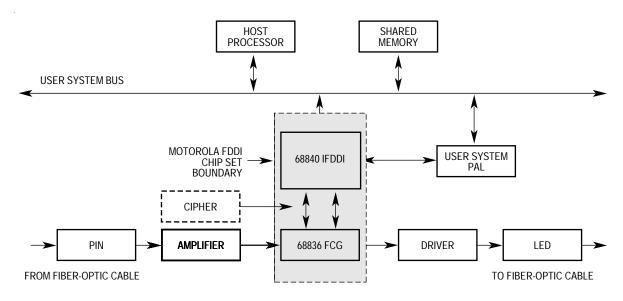

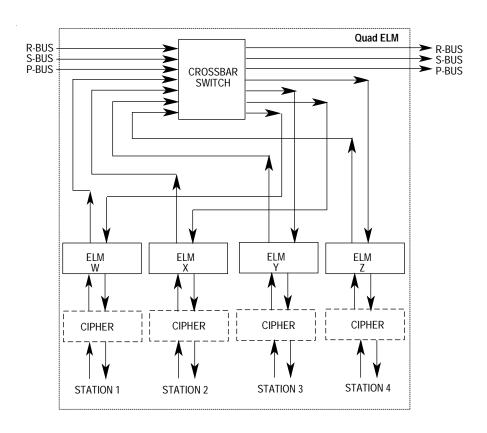

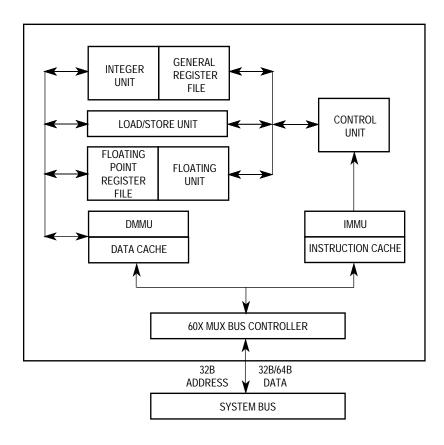

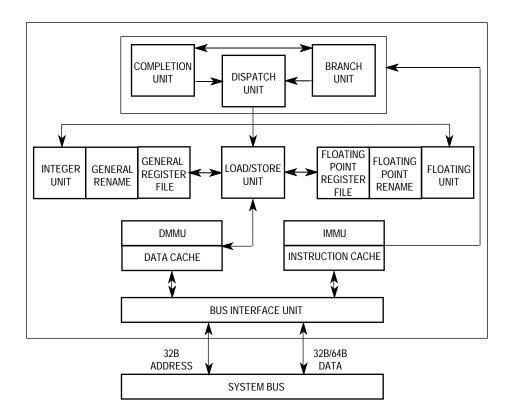

- Low-Power Features: On-Chip Phase Lock Loop (PLL), Low-Power Modes in  $\mu A$  Range