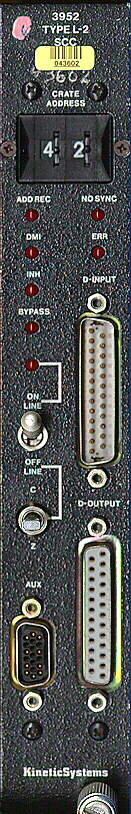

GENERAL DESCRIPTION

The Model 3952 is a double-width Type L-2 Serial Crate Controller (SCC) that provides the inter- face between the CAMAC Serial Highway and the CAMAC Dataway. It fully complies with the CAMAC specifications IEEE 583 and 595. The use of L-2 Crate Controllers with an associated Serial Driver (such as the Model 3992, 3994 or 2050 Series) allows CAMAC crates to be separated by great distances with economical cabling between them.

The 3952 may be operated in bit-serial or byte-serial mode, at the option of the user. A strap is provided for making this selection. Bit-serial operation requires two twisted pair for the Serial Highway, one for the clock and one for the data. Byte-serial operation is a factor of 10 faster and requires nine pair, one for the clock and eight for the data. The Model 3952 will operate at clock rates from arbitrarily slow to 5 MHz. However, the trans- mission medium may well limit the maximum speed. The Serial Highway may be configured by direct connection of the Serial Crate Controllers and the Serial Driver. Use of a bit-serial Unport adapter or a byte-serial Unport adapter at each crate or cluster of crates provides bypass and loop collapse as well as allowing transmission over longer distances at higher speeds than is obtained through direct connection.

DEMAND MESSAGE GENERATION

GENERAL. In response to any L-signal in the crate, the L-2 Crate Controller, if enabled, generates a three-byte Demand message and inserts the message into the data stream. Demand messages are inserted between other messages, and a three-byte memory is inserted in the incoming data stream as Demand messages are transmitted. When a three-byte gap is detected between incoming messages, the delay is switched out, allowing another Demand message to be generated. REPEATED DEMAND MESSAGES. If the L-signal in the crate is not cleared by a predetermined elapsed time, a Repeated-Demand message is generated. Repeated messages have each of the five Graded-L bits set to 1. The repeat-timer can be adjusted for delays between 1 msec and 10 sec. The delay is strap-selected. The timer can also be disabled. SGL CONNECTOR. The rear-panel SGL Connector is a 52-way Cannon double-density connector with pins, Model 5943. This connector has all the input and output signals necessary for encoding the SGL field of the Demand message.

BYPASS AND LOOP COLLAPSE

Relay contacts are provided for control of external Bypass and Loop Collapse devices. The contacts have one side connected to module common and the other to the serial highway connectors. The bypass contact is closed for Bypass, and the loop collapse contact is closed for Loop Collapse. Loss of crate power will cause the bypass contact to close and the loop collapse contact to open.

AUXILIARY CONNECTOR

A 19-pin miniature connector, Model 5941, provides front-panel access for adapter power and for certain test signals. The test signals are: CLOCK IN, CLOCK OUT, BIT DATA IN, BIT DATA OUT, and MESSAGE IN (Delimiter). All signals are TTL, low-true. The MESSAGE IN signal is useful for synchronizing an oscilloscope to the message traffic. Any external wires that are connected to these test signals should be limited to 0.5 meters so that the crate controller's performance is not degraded.

POWER REQUIREMENTS: +6volts-2200mA

|

Command |

SQ |

Action |

F(0)-A(1) RD1 F(1)-A(0) RD2 F(1)-A(12) RD2 F(17)-A(0) WT2 F(19)-A(0) SS2 F(23)-A(0) SC2 |

DSQ 1 1 1 1 1 |

Re-Reads previous read-field Reads status register. Reads LAM pattern. Writes status rigister. Selectively sets status register. Selectively clears Status register. |

|

Bit |

True-State Definition |

State on power-up |

Notes |

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

Initiates Dataway Z Initiates dataway C SCC control-bit for dataway I DERR DSX DSQ Dataway I (reserved) Demand Enable Internal Demand (L24) Loop collapse SCC bypass Dataway off-line Switch off-line (reserved) Selected L's Present |

0 0 1 0 0 0 0 - 0 0 0 1 1 - - - |

write only write only read/write read only read only read only read only ------- read/write read/write read/write write only Writes control-bit, reads actuall state read only ------- read only |