* 8 channels in single-width module

* Four logic outputs per channel

* Direct-coupled

* Output duration equal to input overlap

* Double-pulse resolution < 8 ns

* Stage delay 3 ns

* Within NIM power dissipation requirements

The LRS Model 370 8-Channel Strobed Coincidence accepts standard NIM logic signals at the eight independent logic inputs and the common gate input. Channel inputs which are simultaneous with the common gate signal satisfy the two-fold coincidence condition and generate four NIM level fast logic outputs of duration equal to the overlap time of the coincident signals, and of rise and falltimes less than 2 ns. A full amplitude output will be produced by gate and signal overlap of < 1.8 ns. Since internal delay through the gate circuit is approximately 1 ns longer than through the logic input circuit, the gate signal should precede the logic input by 1 ns to permit accurate coincidence determination of input signals.

The Model 370 is a compact, state-of-the-art design employing MECL Ill integrated circuits to provide coincidence resolving times under 1.8 ns and a maximum rate greater than 125 MHz. The basic simplicity of the Model 370 can be verified by its parts count, manifest in its 3.2 ns input-output delay. Such simplicity of circuit design, coupled with full pretesting and burn-in of all active components, creates a highly stable and reliable instrument coincident with the demanding requirements of today's larger experiments.

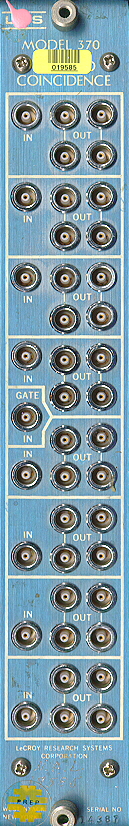

Packaged in a #1 NIM module, the Model 370 provides 8 coincidence channels without exceeding power limits imposed by the NIM standard. Its compactness permits more flexible use of available experimental areas and eliminates the waste of bin space caused by front panel limitations typical of the past.

NIM Model 370 8-CHANNEL STROBED COINCIDENCE

SPECIFICATIONS

|

INPUT CHARACTERISTICS |

|

|

Logic Inputs: |

Eight; one for each of eight independent channels; impedance 50Ohm ; protected to -- 5 volts; -600 mV minimum amplitude; reflections < 7% for inputs of 2 ns risetime. |

|

Gate: |

Common to all eight channels; direct-coupled; -600 mV or greater enables (standard AEC fast logic level); impedance 50Ohm ; protected to +/- 5 volts; reflec- tions < 7% for inputs of 2 ns risetime. Gate input should precede logic inputs by 1 ns to compensate for internal delay. |

|

Slow (Bin) Gate: |

Via rear connector, with rear-panel On-Off switch; risetimes and falltimes ap- proximately 20 ns; quiescently above + 4 volts, clamping to ground inhibits; direct-coupled. |

|

Signal Duration: |

Approximately 2 ns minimum; no maximum. |

|

OUTPUT CHARACTERISTICS |

|

|

Fast Logic Outputs: |

2 bridged current source pairs per channel; each pair quiescently 0 mA, -32 mA during outputs; duration equal to overlap between input logic signal and fast gate. Non-updating. For optimum pulse shape at least one output of each pair must be terminated in 50 Ohm. |

|

Risetimes and Falltimes: |

Risetime, < 2.0 ns typical, 2.5 ns maximum; falltime, < 2.0 ns. All outputs terminated into 50 OHm. |

|

GENERAL |

|

|

Double-Pulse Resolution: |

< 8 ns. |

|

Delay: |

Input-Output, 3.2 ns. |

|

Coincidence Overlap: |

Minimum overlap of 1.8 ns produces full amplitude output. |

|

Packaging: |

In conformance with AEC standard for nuclear modules (AEC Report TID-20893); RF shielded AEC #1 module fitting 12/bin; dimensions 1.375 x 8.75 x 10 inches deep. |

|

Power Requirements: |

-6 V at 260 mA; |