azonenberg:micrel:ksz9021rn

This is an old revision of the document!

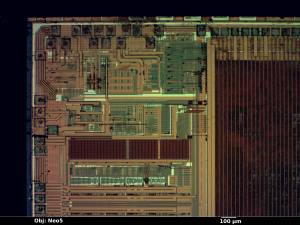

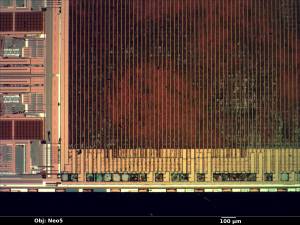

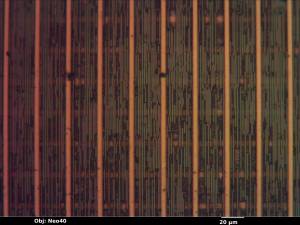

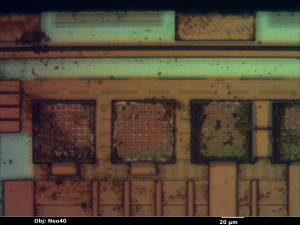

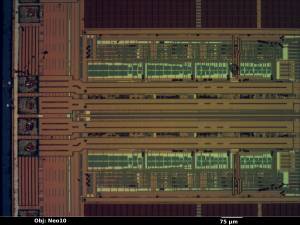

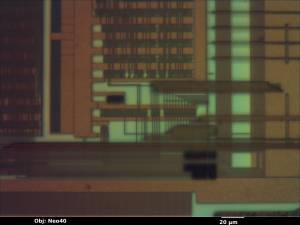

10/100/1000 Ethernet PHY. Process tech looks to be around 180nm with at least five metal layers.

UPDATE: Confirmed by IBIS model (http://www.micrel.com/_Models/IBIS/KSZ9021RN/k9021rn.ibs) to be 150nm TSMC.

Full datasheet from TMSC for the particular I/O cells in use: http://www-afs.secure-endpoints.com/afs/ece/u/blevine/TSMC_IO.pdf

Package

Die

azonenberg/micrel/ksz9021rn.1420169314.txt.gz · Last modified: 2015/01/02 03:28 by azonenberg