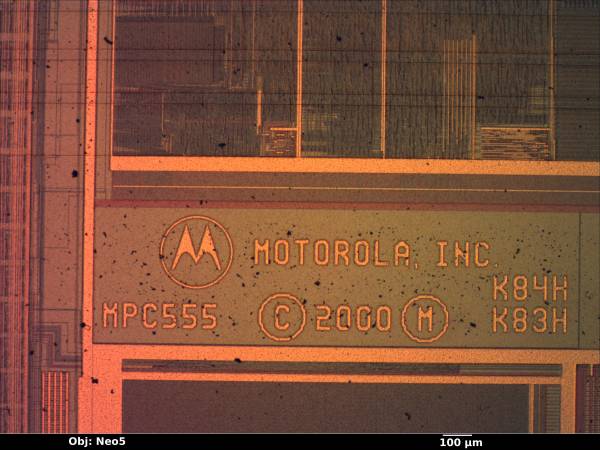

Found in unknown_car_mcm as a bare die but was labeled.

Not known what the geometry size of CDR1 process is.

Google indicates the MPC555 is a Freescale part but the die says Motorola. Tagging as both.

From datasheet:

- PowerPC core with floating-point unit

- 26 Kbytes fast RAM and 6 Kbytes TPU microcode RAM

- 448 Kbytes Flash EEPROM with 5-V programming

- 5-V I/O system

- Serial system: queued serial multi-channel module (QSMCM), dual CAN 2.0B controller

- 50-channel timer system: dual time processor units (TPU3), modular I/O system (MIOS1)

- 32 analog inputs: dual queued analog-to-digital converters (QADC64)

- Submicron HCMOS (CDR1) technology

- 272-pin plastic ball grid array (PBGA) packaging

- 40-MHz operation, -40 °C to 125 °C with dual supply (3.3 V, 5 V) (-55 °C to 125 °C for the suffix A device)

- 32-bit architecture (PowerPC ISA architecture compliant)

- Core performance measured at 52.7-Kbyte Dhrystones (v2.1) @ 40 MHz

- Fully static, low power operation

- Integrated double-precision floating-point unit

- Precise exception model